BULLETIN OF THE POLISH ACADEMY OF SCIENCES TECHNICAL SCIENCES, Vol. 65, No. 5, 2017 DOI: 10.1515/bpasts-2017-0062

## Cascaded multilevel converters in recent research and applications

#### M. MALINOWSKI

Institute of Control and Industrial Electronics, Warsaw University of Technology, 75 Koszykowa St., 00-662 Warsaw, Poland

Abstract. Multilevel converters have been intensively investigated and developed since 1960s and have found successful industrial applications. The aim of this paper is to present state of the art as well as recent research and applications of cascaded multilevel converters, which are a very interesting solution for power distribution systems and renewable energy sources. Cascaded multilevel converters can easily operate at medium and high voltage based on the series connection of power modules (cells), which use standard low-voltage component configurations. Series connections of modules (cells) allow for high quality output voltages and input currents, reduction of passive components and availability of component redundancy. Due to these features the cascaded multilevel converters have been recognized as attractive solutions for high-voltage direct-current (HVDC) transmission, solid state transformers (SST) and photovoltaic (PV) systems.

Key words: multilevel converters, cascaded converters, modular multilevel converters, modulation, solid state transformer, photovoltaic systems.

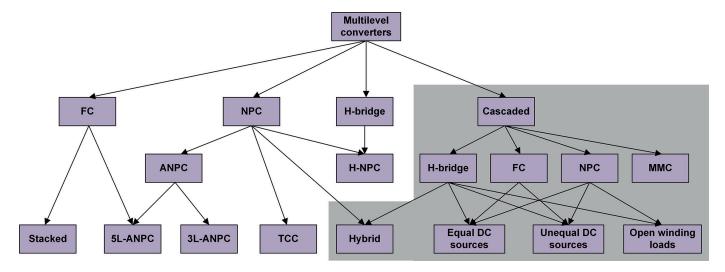

Fig. 1. Classification of the most popular multilevel converters

#### 1. Introduction

Lately, multilevel power electronics converters have become a very important part of energy conversion in drives, distributed energy systems and renewable energy sources [1].

There are many types of multilevel voltage source converters, which are shown in Fig. 1 and described in [1]. The multilevel converter is not a new topology, some converters are known since the 1960s, but they were not used in industry until recently because of certain technical barriers. There are many types of multilevel converters and are increasingly frequently used in power conversion systems due to distinctive advantages

Manuscript submitted 2017-04-18, revised 2017-06-08, initially accepted for publication 2017-06-08, published in October 2017.

for multilevel structures. Among the main benefits one may count a superior harmonic spectrum for a given switching frequency, a lower dv/dt stress at the converter terminals, cables and end windings of transformers/generators, a lower common mode voltage, and substantially lower semiconductor switching losses, particularly at medium to higher switching frequencies. A three-level topology is also a highly competitive alternative to the two-level structure in terms of cost, efficiency, and weight/size [2].

The final choice of converter topology for RES depends on type of application, expected power, reliability demand and price. Three-phase multilevel converters, e.g. three-level neutral point clamped (3L-NPC) [3–6], three-level transistor clamped (3L-TCC) [4] or five-level active neutral point clamped (5L-ANPC) [7–9] are most popular in high power applications. However, 3L-NPC converters may be considered even in power range of few hundreds kVA, which was discussed in [2].

<sup>\*</sup>e-mail: malin@isep.pw.edu.pl

Recently, many publications have addressed multilevel converter technology and stressed the growing importance of them for cascaded multilevel converters (CMC) applied in high power wind turbines, wind parks [10–15], photovoltaic and power systems [34] – the main topic of this publication.

#### 2. Multilevel converter topologies

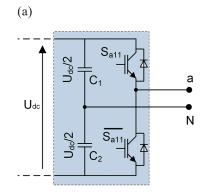

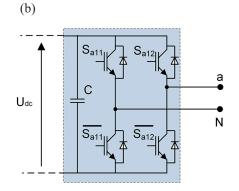

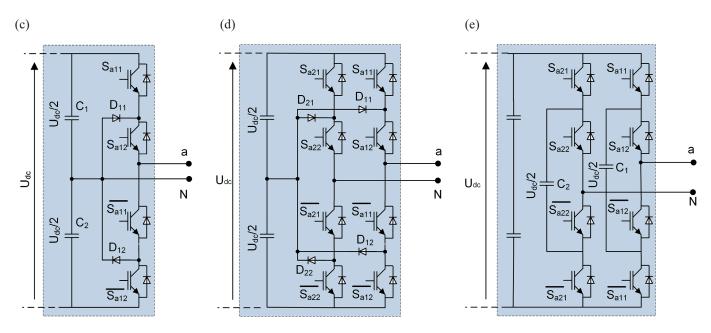

2.1. Basic converter topologies (cells). Several topologies can be used as a single converter or module in cascade configuration, which is shown in Fig. 2. The most popular solution is the full-bridge three-level converter, also known as H-bridge converter (Fig. 2b), which can generate zero states and has lower DC-link voltage level as compared with half-bridge two-level converter (Fig. 2a). Nowadays, half-bridge and full bridge multilevel converters composed of 3L-NPC or 3L-FC, shown in Fig. 2c-e, are significantly growing in importance. They are known as half-bridge 3L-NPC, full-bridge 5L-NPC and full-bridge 5L-FC [16]. All those converters have zero voltage states, but the half-bridge 3L-NPC topology requires

higher DC-link voltage level as compared with 5L-NPC and 5L-FC. All possible switching states for topologies from Fig. 2 are shown in Table 1.

Table 1 Switching states for converter from Fig. 2

|                       | Converter switching states              |           |          |   |  |  |  |  |

|-----------------------|-----------------------------------------|-----------|----------|---|--|--|--|--|

| Voltage level         | $Sa_{11}$ $Sa_{12}$ $Sa_{21}$ $Sa_{22}$ |           |          |   |  |  |  |  |

| half-bridge two-level |                                         |           |          |   |  |  |  |  |

| $+U_{dc}/2$           | 1                                       | _         | _        | _ |  |  |  |  |

| $-U_{dc}/2$           | 0                                       | _         | _        | _ |  |  |  |  |

| full-brid             | ge three-                               | -level (H | -bridge) |   |  |  |  |  |

| $+U_{dc}$             | 0                                       | 1         | _        | - |  |  |  |  |

| 0                     | 0                                       | 0         | _        | _ |  |  |  |  |

| U                     | 1                                       | 1         | _        | _ |  |  |  |  |

| $-U_{dc}$             | 1                                       | 0         | _        | _ |  |  |  |  |

Fig. 2. Basic converter modules (cells) (a) half-bridge two-level (b) full-bridge three-level (H-bridge) (c) half-bridge three-level NPC (d) full-bridge five-level NPC (e) full-bridge five-level FC

$\label{eq:Table 1} Table \ 1$  Switching states for converter from Fig. 2 – cont.

| Converter switching states |                                         |          |     |   |  |  |  |  |  |

|----------------------------|-----------------------------------------|----------|-----|---|--|--|--|--|--|

| Voltage level              | $Sa_{11}$ $Sa_{12}$ $Sa_{21}$ $Sa_{22}$ |          |     |   |  |  |  |  |  |

| half-b                     | ridge th                                | ee–level | NPC |   |  |  |  |  |  |

| $+U_{dc}/2$                | 1                                       | 1        | _   | _ |  |  |  |  |  |

| 0                          | 0                                       | 1        | _   | _ |  |  |  |  |  |

| $-U_{dc}/2$                | 0                                       | 0        | -   | - |  |  |  |  |  |

| full-bridge five-level NPC |                                         |          |     |   |  |  |  |  |  |

| $+U_{dc}$                  | 1                                       | 1        | 0   | 0 |  |  |  |  |  |

| $+U_{dc}/2$                | 1                                       | 1        | 0   | 1 |  |  |  |  |  |

| $^{+}O_{dc}/^{2}$          | 0                                       | 1        | 0   | 0 |  |  |  |  |  |

|                            | 1                                       | 1        | 1   | 1 |  |  |  |  |  |

| 0                          | 0                                       | 0        | 0   | 0 |  |  |  |  |  |

|                            | 0                                       | 1        | 0   | 1 |  |  |  |  |  |

| $-U_{dc}/2$                | 0                                       | 0        | 0   | 1 |  |  |  |  |  |

| $-O_{dc}/2$                | 0                                       | 1        | 1   | 1 |  |  |  |  |  |

| $-U_{dc}$                  | 0                                       | 0        | 1   | 1 |  |  |  |  |  |

| full-                      | bridge f                                | ve–level | FC  |   |  |  |  |  |  |

| $+U_{dc}$                  | 1                                       | 1        | 0   | 0 |  |  |  |  |  |

|                            | 1                                       | 0        | 0   | 0 |  |  |  |  |  |

| $+U_{dc}/2$                | 0                                       | 1        | 0   | 0 |  |  |  |  |  |

| $^{+}O_{dc}/^{2}$          | 1                                       | 1        | 0   | 1 |  |  |  |  |  |

|                            | 1                                       | 1        | 1   | 0 |  |  |  |  |  |

|                            | 0                                       | 0        | 0   | 0 |  |  |  |  |  |

|                            | 1                                       | 1        | 1   | 1 |  |  |  |  |  |

| 0                          | 1                                       | 0        | 1   | 0 |  |  |  |  |  |

| U                          | 0                                       | 1        | 0   | 1 |  |  |  |  |  |

|                            | 0                                       | 1        | 1   | 0 |  |  |  |  |  |

|                            | 1                                       | 0        | 0   | 1 |  |  |  |  |  |

|                            | 0                                       | 0        | 0   | 1 |  |  |  |  |  |

| $-U_{dc}/2$                | 0                                       | 0        | 1   | 0 |  |  |  |  |  |

| Odc/ 2                     | 0                                       | 1        | 1   | 1 |  |  |  |  |  |

|                            | 1                                       | 0        | 1   | 1 |  |  |  |  |  |

| $-U_{dc}$                  | 0                                       | 0        | 1   | 1 |  |  |  |  |  |

**2.2. CMC topologies.** Multilevel converters are still being developed in spite of the fact that the first multilevel topology known as series connected H-bridge or cascaded H-bridge was invented in the late 1960s [17]. This was closely followed by the development of FC [18] and NPC [19]. Recent advances in single-phase multilevel converter topologies focus mainly

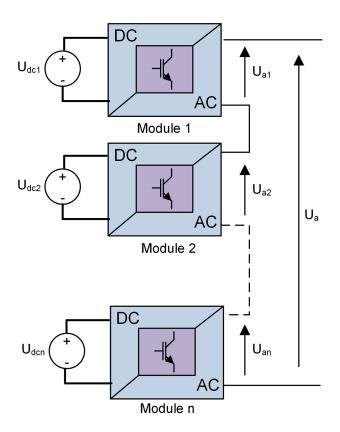

Fig. 3. Structure view of one-phase cascade multilevel PWM converter

on hybrid technology based on series connection of modules (Fig. 3), different classic topologies (e.g. those shown in Fig. 2), DC voltage levels and modulation [16]. The output voltage is obtained by adding the voltages of each module:

$$u_a(t) = u_{a1}(t) + u_{a2}(t) + \dots + u_{an}(t).$$

(1)

The number of levels obtained in such a cascade multilevel converter with equal DC voltage ratios on each module can be described as [16]:

$$m = 1 + \sum_{j=1}^{n} (m_j - 1).$$

(2)

where  $m_j$  is the number of phase-to-neutral voltage levels of each module. An example of possible switching states for cascade connection of two H-bridge converters is shown in Table 2.

Usually, cascaded multilevel converters use the same DC-link voltage value for each module. However, a larger number of levels can be obtained not only by increasing number of modules, but even by applying unequal DC voltage ratios between them, which eliminates some or even all voltage level redundant switching states in the converter. The topologies having different DC-link voltages ratios are called asymmetric cascaded converters; this concept was introduced in [20]. Later this idea was

Table 2

Switching states and voltage levels for two 5L-CHB converters with 1:1 DC voltage ratio

| 1:1 d         | Converter switching states |           |                  |                  |                  |                  |

|---------------|----------------------------|-----------|------------------|------------------|------------------|------------------|

| Voltage level | Module 1                   | Module 2  | Sa <sub>11</sub> | Sa <sub>12</sub> | Sa <sub>21</sub> | Sa <sub>22</sub> |

| $+2U_{dc}$    | $+U_{dc}$                  | $+U_{dc}$ | 0                | 1                | 0                | 1                |

|               | $+U_{dc}$                  | 0         | 0                | 1                | 1                | 1                |

| ⊥ <b>I</b> I  | $+U_{dc}$                  | 0         | 0                | 1                | 0                | 0                |

| $+U_{dc}$     | 0                          | $+U_{dc}$ | 1                | 1                | 0                | 1                |

|               | 0                          | $+U_{dc}$ | 0                | 0                | 0                | 1                |

|               | 0                          | 0         | 0                | 0                | 1                | 1                |

|               | 0                          | 0         | 0                | 0                | 0                | 0                |

| 0             | 0                          | 0         | 1                | 1                | 1                | 1                |

| U             | 0                          | 0         | 1                | 1                | 0                | 0                |

|               | $+U_{dc}$                  | $-U_{dc}$ | 0                | 1                | 1                | 0                |

|               | $-U_{dc}$                  | $+U_{dc}$ | 1                | 0                | 0                | 1                |

|               | $-U_{dc}$                  | 0         | 1                | 0                | 1                | 1                |

| <b>1</b> 1    | $-U_{dc}$                  | 0         | 1                | 0                | 0                | 0                |

| $-U_{dc}$     | 0                          | $-U_{dc}$ | 1                | 1                | 1                | 0                |

|               | 0                          | $-U_{dc}$ | 0                | 0                | 1                | 0                |

| $-2U_{dc}$    | $-U_{dc}$                  | $-U_{dc}$ | 1                | 1                | 0                | 0                |

further explored for MV converters [21] with two or more modules in series with a voltage ratio asymmetry  $(1:2:::2^{n-1})$ , capable of generating 7 different voltage levels with only two three-level modules (Table 3).

Later voltage ratios of three  $(1:3:::3^{n-1})$  for three-level modules (Table 3) [21–22] and four  $(1:4:::4^{n-1})$  for fivelevel modules [12-13] were introduced, eliminating all redundancies and maximizing the number of levels at the output. A comprehensive work analyzing this topology in depth is presented in [16, 23]. Besides the exponential increase in the number of levels when adding more modules, cascade topology allows to switch the highest voltage module at fundamental frequency, reducing the switching losses of the converter and improving efficiency. It is also worth to note that unequal DC voltage ratios among modules bring unequal power distribution among them. Therefore the high voltage module manages the major part of the output power. Due to this power distribution, these kinds of converters can be designed with different switch technologies like IGCT for the high power converter, HV-IGBT for the medium power converter and LV-IGBT for the low power converter. Cascaded multilevel inverters that use different switch technologies are also called hybrid cascaded inverters [16, 23–30]. One of the main drawbacks of this topology is the loss of modularity due to the different semiconductor technology used [12].

If the topology shown in Fig. 3 is fed with unequal DC voltage ratios between modules, the number of levels can be described by equation (3) [16]:

Table 3

Switching states and voltage levels for two CHB Converters with 1:2 and 1:3 DC voltage ratio

| 1:2 d         | lc voltage rati | .0                        | 1:3 d         | c voltage rati | 0          | Converter switching states |           |           |                  |

|---------------|-----------------|---------------------------|---------------|----------------|------------|----------------------------|-----------|-----------|------------------|

| Voltage level | Module 1        | Module 2                  | Voltage level | Module 1       | Module 2   | Sa <sub>11</sub>           | $Sa_{12}$ | $Sa_{21}$ | Sa <sub>22</sub> |

| $+3U_{dc}$    | $+U_{dc}$       | $+2U_{dc}$                | $+4U_{dc}$    | $+U_{dc}$      | $+3U_{dc}$ | 0                          | 1         | 0         | 1                |

| 1211          | 0               | $+2U_{dc}$                | 1211          | 0              | $+3U_{dc}$ | 0                          | 0         | 0         | 1                |

| $+2U_{dc}$    | 0               | $+2U_{dc}$                | $+3U_{dc}$    | 0              | $+3U_{dc}$ | 1                          | 1         | 0         | 1                |

|               | $-U_{dc}$       | $+2U_{dc}$                | $+2U_{dc}$    | $-U_{dc}$      | $+3U_{dc}$ | 1                          | 0         | 0         | 1                |

| $+U_{dc}$     | $+U_{dc}$       | 0                         | _II           | $+U_{dc}$      | 0          | 0                          | 1         | 0         | 0                |

|               | $+U_{dc}$       | 0                         | $+U_{dc}$     | $+U_{dc}$      | 0          | 0                          | 1         | 1         | 1                |

|               | 0               | 0                         | 0             | 0              | 0          | 0                          | 0         | 0         | 0                |

| 0             | 0               | 0                         |               | 0              | 0          | 1                          | 1         | 0         | 0                |

| 0             | 0               | 0                         | 0             | 0              | 0          | 0                          | 0         | 1         | 1                |

|               | 0               | 0                         |               | 0              | 0          | 1                          | 1         | 1         | 1                |

|               | $-U_{dc}$       | 0                         | II            | $-U_{dc}$      | 0          | 1                          | 0         | 1         | 1                |

| $-U_{dc}$     | $-U_{dc}$       | 0                         | $-U_{dc}$     | $-U_{dc}$      | 0          | 1                          | 0         | 0         | 0                |

|               | $U_{dc}$        | -2 <i>U</i> <sub>dc</sub> | $-2U_{dc}$    | $+U_{dc}$      | $-3U_{dc}$ | 0                          | 1         | 1         | 0                |

| $-2U_{dc}$    | 0               | -2 <i>U</i> <sub>dc</sub> | 311           | 0              | $-3U_{dc}$ | 1                          | 1         | 1         | 0                |

| $-2O_{dc}$    | 0               | -2 <i>U</i> <sub>dc</sub> | $-3U_{dc}$    | 0              | $-3U_{dc}$ | 0                          | 0         | 1         | 0                |

| $-3U_{dc}$    | $-U_{dc}$       | -2 <i>U</i> <sub>dc</sub> | $-4U_{dc}$    | $-U_{dc}$      | $-3U_{dc}$ | 1                          | 0         | 1         | 0                |

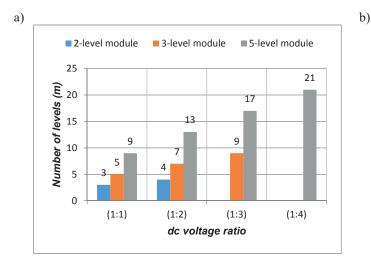

Fig. 4. Maximum number of levels for two (a) and three (b) cascade connected modules based on two-, three-, or five-level converters with different DC source ratios

$$m = 1 + \sum_{j=1}^{n} (m_j - 1) \cdot V_{dcj}$$

(3)

where  $V_{dcj}$  is defined as dc voltage ratios between modules, e.g.  $1:2:::2^{n-1}$ .

Figure 4 shows the maximum number of levels in cascaded multilevel converter using two or three modules of two-, three-and five-level converters.

#### 3. Modulation of CMC

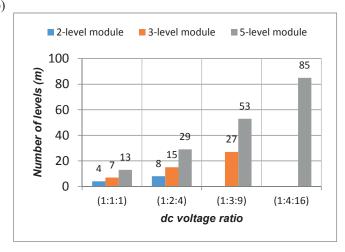

The most interesting type of modulation for CMC is quasi space vector modulation (SVM). This kind of modulator was proposed in [31] for single-phase 3L-NPC converter controlled in virtual synchronous rotating coordinate system. Then quasi SVM developed in [32–33] was applied for all kinds of multilevel converters and called one-dimensional modulation (1DM). Basic idea of this simple modulation come from three-phase two-level converters, where duty cycle of each phase can be calculated as  $u_{a\_ref}/u_{dc}+T_s/2$ , where  $u_{a\_ref}$  is reference voltage for modulator,  $u_{dc}$  is DC link voltage, and  $T_s$  is sampling time. This idea can be easily applied in single-phase multilevel converters, where modulation method uses the nearest switching

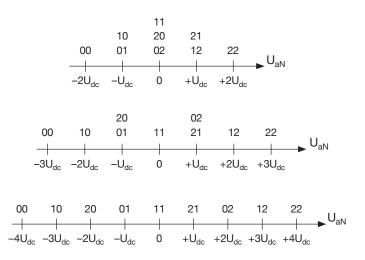

Fig. 5. 1-D representation of switching states in 5L-NPC

states (voltage levels) to the reference  $u_{a\_ref}$  with the aim to generate switching sequence and duty cycle. Switching states of 5L-NPC, 5L-FLC and 5L-CHB based on Table 1 can be shown in 1-D representation (Fig. 5), where each digit of switching states  $S_1S_2$  represents one leg (5L-NPC, 5L-FLC) or one module (5L-CHB) of converter and the value of each digit in switching state varies with level of leg output voltage (e.g.  $S_1 = 0$  for lowest possible output voltage of leg "1" in 5L-NPC converter equal  $-U_{dc}/2$  or  $S_1 = 2$  for highest possible output voltage of leg "1" equal  $U_{dc}/2$ ). It is worth to note that same notation can be used for any number of one leg levels N giving maximal value of S = N - 1.

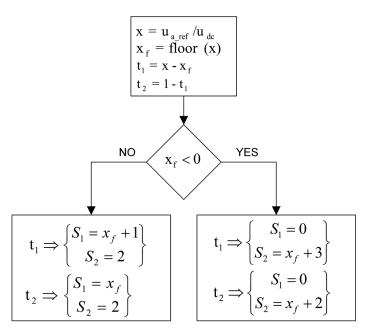

The flowchart of the 1DM method for 5L-NPC is shown in Fig. 6, where  $x = u_{a \ ref}/(u_{dc}/2)$  is the normalization of the

Fig. 6. Flowchart of 1-DM for 5L-NPC

reference to the nearest output voltage levels and operator  $x_f = floor(x)$  means round to the integer towards minus infinity (e.g. 1, 0, -1, -2 for five-level converter) [32]. Finally,  $x_f$  algorithm determines switching sequence and duty cycles. The same flowchart can be used for 5L-FC converter, taking in account the fact that there are twice as many redundant switching states for this type of converter and some of them cannot be used (Table 4). The only difference is that signals  $S_1S_2$  from Fig. 6 are related to different power switches.

Table 4

Switching states for 5L-NPC and 5L-FC

|               | Converter switching states |           |                  |                  |          |  |  |  |

|---------------|----------------------------|-----------|------------------|------------------|----------|--|--|--|

| Voltage level | Sa <sub>11</sub>           | $Sa_{12}$ | Sa <sub>21</sub> | Sa <sub>22</sub> | $S_1S_2$ |  |  |  |

| full-         | bridge fiv                 |           |                  |                  |          |  |  |  |

| $+U_{dc}$     | 1                          | 1         | 0                | 0                | 20       |  |  |  |

| 11. /2        | 1                          | 1         | 0                | 1                | 21       |  |  |  |

| $+U_{dc}/2$   | 0                          | 1         | 0                | 0                | 10       |  |  |  |

|               | 1                          | 1         | 1                | 1                | 22       |  |  |  |

| 0             | 0                          | 0         | 0                | 0                | 00       |  |  |  |

|               | 0                          | 1         | 0                | 1                | 11       |  |  |  |

| 11 /2         | 0                          | 0         | 0                | 1                | 01       |  |  |  |

| $-U_{dc}/2$   | 0                          | 1         | 1                | 1                | 12       |  |  |  |

| $-U_{dc}$     | 0                          | 0         | 1                | 1                | 02       |  |  |  |

| full-         | -bridge fi                 | ive-leve  | l FC             |                  |          |  |  |  |

| $+U_{dc}$     | 1                          | 1         | 0                | 0                | 20       |  |  |  |

|               | 1                          | 0         | 0                | 0                | 10       |  |  |  |

| 111 /2        | 0                          | 1         | 0                | 0                | 10       |  |  |  |

| $+U_{dc}/2$   | 1                          | 1         | 0                | 1                | 21       |  |  |  |

|               | 1                          | 1         | 1                | 0                | 21       |  |  |  |

|               | 0                          | 0         | 0                | 0                | 00       |  |  |  |

|               | 1                          | 1         | 1                | 1                | 22       |  |  |  |

| 0             | 1                          | 0         | 1                | 0                | 11       |  |  |  |

| U             | 0                          | 1         | 0                | 1                | 11       |  |  |  |

|               | 0                          | 1         | 1                | 0                | 11       |  |  |  |

|               | 1                          | 0         | 0                | 1                | 11       |  |  |  |

|               | 0                          | 0         | 0                | 1                | 01       |  |  |  |

| 11 /2         | 0                          | 0         | 1                | 0                | 01       |  |  |  |

| $-U_{dc}/2$   | 0                          | 1         | 1                | 1                | 12       |  |  |  |

|               | 1                          | 0         | 1                | 1                | 12       |  |  |  |

| $-U_{dc}$     | 0                          | 0         | 1                | 1                | 02       |  |  |  |

Another interesting feature of multilevel converter is the redundancy of some switching states, shown in Fig. 5, which can be used for capacitor voltage balancing, reduction of

switching losses and minimization of common mode voltage. 1DM is not taken in account in the basic flowchart shown in Fig. 6. Therefore, an additional algorithm has to take in account some optimization, as shown in Table 5 for 5L-NPC and Table 6 for 5L-FC.

Table 5

Redundant switching states for capacitor voltage balancing in 5L-NPC

|                                                   |                      | Con               | verter           | switch    | hing st          | ates             |          |

|---------------------------------------------------|----------------------|-------------------|------------------|-----------|------------------|------------------|----------|

| Voltage<br>level                                  | Capacitor<br>Voltage | Output<br>Current | Sa <sub>11</sub> | $Sa_{12}$ | Sa <sub>21</sub> | Sa <sub>22</sub> | $S_1S_2$ |

| $+u_{dc}/2$ $Uc_1 - Uc_2 \ge 0$ $Uc_1 - Uc_2 < 0$ | $i_a \ge 0$          | 1                 | 1                | 0         | 1                | 21               |          |

|                                                   | $CC_1 - CC_2 \geq 0$ | $i_a < 0$         | 0                | 1         | 0                | 0                | 10       |

|                                                   | Ho Ho < 0            | $i_a \ge 0$       | 0                | 1         | 0                | 0                | 10       |

|                                                   | $Cc_1 - Cc_2 < 0$    | $i_a < 0$         | 1                | 1         | 0                | 1                | 21       |

|                                                   | $Uc_1 - Uc_2 \ge 0$  | $i_a \ge 0$       | 0                | 0         | 0                | 1                | 01       |

|                                                   |                      | $i_a < 0$         | 0                | 1         | 1                | 1                | 12       |

| $-u_{dc}/2$ $Uc_1 - Uc_2 < 0$                     | IIa IIa < 0          | $i_a \ge 0$       | 0                | 1         | 1                | 1                | 12       |

|                                                   | $i_a < 0$            | 0                 | 0                | 0         | 1                | 01               |          |

Table 6

Redundant switching states for capacitor voltage balancing in 5L-FC

|                            |                      |                   |                  | verter           | switcl           | hing st          | ates     |

|----------------------------|----------------------|-------------------|------------------|------------------|------------------|------------------|----------|

| Voltage<br>level           | Capacitor<br>Voltage | Output<br>Current | Sa <sub>11</sub> | Sa <sub>12</sub> | Sa <sub>21</sub> | Sa <sub>22</sub> | $S_1S_2$ |

|                            | $Uc_1 \ge u_{dc}/2$  | $i_a \ge 0$       | 0                | 1                | 0                | 0                | 10       |

| +11 /2                     |                      | $i_a < 0$         | 1                | 0                | 0                | 0                | 10       |

| $+u_{dc}/2$                | $Uc_1 < u_{dc}/2$    | $i_a \ge 0$       | 1                | 0                | 0                | 0                | 10       |

|                            |                      | $i_a < 0$         | 0                | 1                | 0                | 0                | 10       |

|                            | $Uc_1 \ge u_{dc}/2$  | $i_a \ge 0$       | 0                | 1                | 1                | 1                | 12       |

| /2                         |                      | $i_a < 0$         | 1                | 0                | 1                | 1                | 12       |

| $-u_{dc}/2$ $Uc_1 < \iota$ | 11a < 11 /2          | $i_a \ge 0$       | 1                | 0                | 1                | 1                | 12       |

|                            | $u_{dc}/2$           | $i_a < 0$         | 0                | 1                | 1                | 1                | 12       |

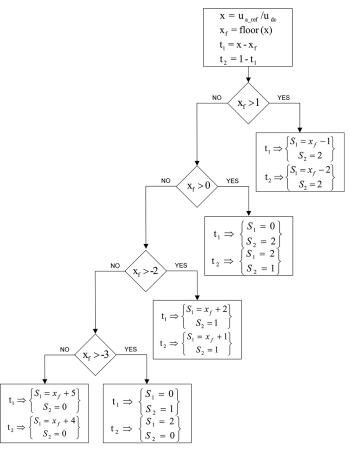

Interesting cases of 1DM operation are the symmetric and asymmetric CHB converters. 1D representation of those converters for two modules with DC voltage ratios 1:1, 1:2 and 1:3 are shown in Fig. 7. Note that converters with DC voltage ratio 1:2 and 1:3 eliminate some or all redundant states. Flowcharts of modulation are shown in Figs. 8–10. A similar idea of 1DM modulation for asymmetric cascaded connected converters can be used in any kind of modules (Fig. 2), giving similar results as previously described multicarrier based hybrid modulation. A detailed description of 1DM can be found in [23, 31–33].

Fig. 7. 1-D representation of switching states in symmetric and asymmetric CHB converters

Fig. 8. Flowchart of 1-DM for DC voltage ratio 1:1

#### 4. CMC in recent research and applications

**4.1. Applications in power distribution system.** A converter operating at medium voltage (MV) level should be designed as a modular converter [34]. The modularity of cascaded topology allows for easy expansion of converter unit for a desired voltage level by increasing the number of modules.

Current state-of-art semiconductor devices are still not ready to operate with MV, therefore, applicable solutions include to-pologies of cascade connected multi-level converters, forming MV waveform. Cascaded topology provides high switching frequency, while maintaining relatively low switching losses, since

Fig. 9. Flowchart of 1-DM for DC voltage ratio 1:2

Fig. 10. Flowchart of 1-DM for DC voltage ratio 1:3

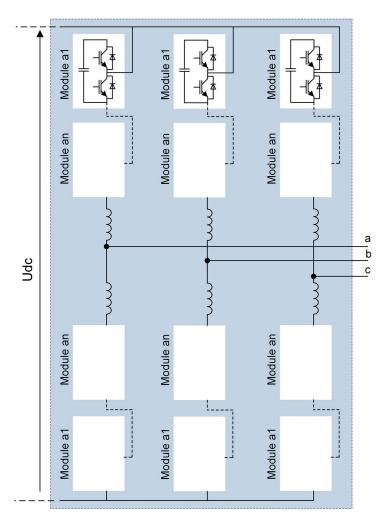

Fig. 11. Three-phase modular multilevel converter

modules do not modulate at the same time. In case of damage of one of transistors in any module, multilevel cascaded converter designed with adequate voltage reserve should be able to work properly, but with less voltage levels.

Therefore, new research on CMC is devoted to several new areas. A cascaded multilevel converter that has recently found industrial applications in HVDC systems is the modular multilevel converter (MMC). This topology, developed by R. Marquardt [35–36], is basically composed of half-bridge two-level modules (Fig. 11) or full-bridge three-level (H-bridge) modules [37–38], which contain low voltage capacitors – a major advantage of this solution. Each phase leg includes modules divided into two equal parts and inductors protecting short circuits. The two switches of the power cell are controlled with complementary signals and produce two active switching states that can connect or bypass its respective capacitor to the total sum of capacitors of the converter leg, generating, in this way, the multilevel waveform. There is a third switching state: both switches are off during startup or fault conditions, allowing the current to freely circulate through the diodes (and through capacitors, if so demanded by the current polarity) [1, 34]. In practical application, there is an additional bypass switch to fully isolate each cell for fault-tolerant operation [39]. An important problem is the control needed to keep each capacitor in constant cell voltage level [36]. An attractive feature of this topology is its modularity and scalability to easily reach medium- and high-voltage levels, while greatly improving AC side power quality, as compared with the classic series connection of power switches in a two-level converter configuration used in HVDC [1, 34]. This topology can be found in practical applications reported with 200 power-cell/phase reaching up to 400 MW [39] and is commercialized by ABB and Siemens as HVDC Light up to 1 GW [5–6].

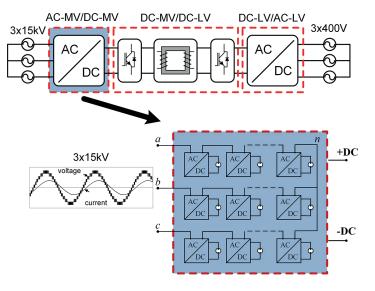

A similar feature of CMC can be used in medium voltage side of solid state transformer (SST), also called smart transformer (Fig. 12). The application of power electronic converters as distribution transformers has become a wide area of interest of many research centers [40–43]. Although SST structure is much more complex as compared to the conventional transformer, it may eliminate some of its disadvantages and add completely new functionalities, e.g.:

- direct connection of DC grid and energy storages, what eliminates additional DC/AC power converters and improving overall efficiency;

- proper operation at voltage unbalance and distortion, that will not be transferred from one side of the transformer to the other;

- increased efficiency of smart grid due to controlled power distribution (reduced energy losses during transmission);

- reactive power and higher-harmonics compensation independently for both sides of transformer;

- easy communication with other elements of the power system (data exchange with other devices, which enables

Fig. 12. Block scheme of SST including: medium voltage AC-MV/DC-MV converter, medium/low voltage MV-DC/DC-LV converter with high frequency intermediate transformer and low voltage DC-LV/AC-LV converter

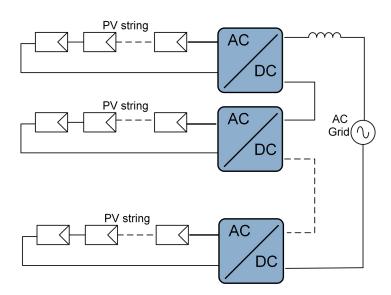

Fig. 13. Applications of single-phase DC/AC converters for multi PV strings used in cascaded converter configuration

fast control of energy flow, reconfiguration of the power grid in case of failure),

• full control of each individual phase and simple island mode of operation.

Other considered applications of CMC are renewable energy sources (RES), mainly PV, where each converter module requires an isolated DC voltage obtained from photovoltaic panels, which is shown in Fig. 13. This structure is capable of reaching medium output voltage levels using only standard low voltage mature technology components, as well as minimizing total harmonic distortion THD, which can provide significant reduction of output passive filters. This kind of converters also features a high modularity degree because each converter can be seen as a module with similar circuit topology, control structure and modulation [16, 34, 44]. Thus, in case of a fault in one of these modules, it is possible to replace it quickly and easily. Moreover, with an appropriated control strategy it is possible to bypass the faulty module without stopping the load, bringing an almost continuous overall availability [47].

# **4.2. Examples of CMC operation.** As stated before, the most important features of CMC can be summarized as follows.

- The structure is capable of reaching medium output voltage levels using only standard low voltage mature technology components.

- The topology allows for easy expansion of converter unit for desired voltage level by increasing the number of modules.

- Converters are designed with adequate voltage reserve, so in case of damage of one of the transistors in any module, they should be able to work properly, although with less voltage levels.

- The converter is capable of proper post-fault operation thanks to easy reconfiguration mechanism.

- The topology achieves high switching frequency, while maintaining relatively low switching losses.

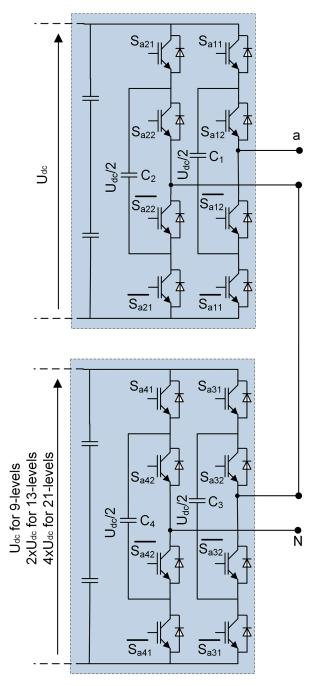

Fig. 14. Scheme of two cascade connected 5L FC modules (cells)

The topology minimizes total harmonic distortion THD of voltage and current, which can provide a significant reduction of output passive filters.

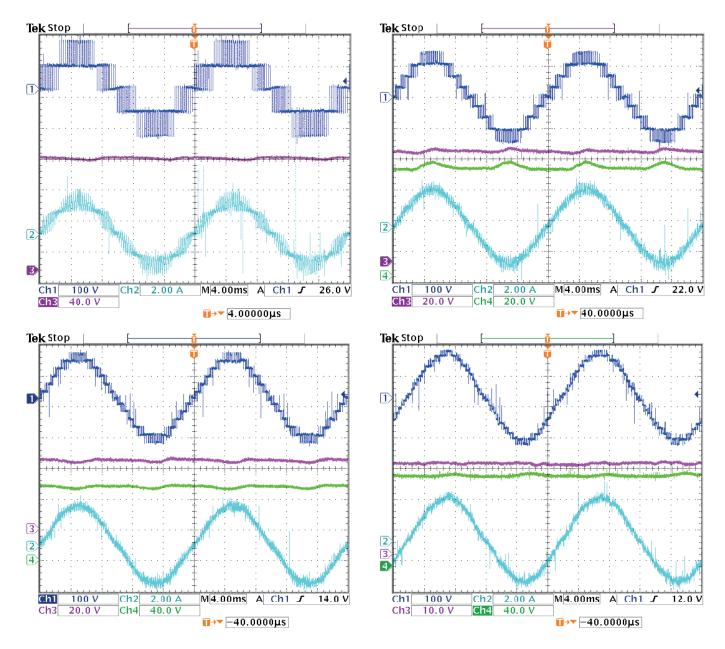

Some of those features can be presented on exemplary scheme of two cascade connected 5-level FC modules shown in Fig. 14. High performance of steady state operation of 5-, 9-, 13- and 21-level converters is presented in Fig. 15. In all cases the current is very smooth, with low harmonic content. Output voltage waveform of 13- and 21-level converters is nearly sinusoidal. Therefore, output LC filter in some applications can be omitted.

Fig. 15. Experimental results of single-phase multilevel converter based on FC modules: (a) 5-level (b) 9-level (c) 13-level (d) 21-level. From the top: converter output voltage  $u_a$ , DC-link voltage  $u_{dc1}$  and  $u_{dc2}$ , output current  $i_a$  [48]

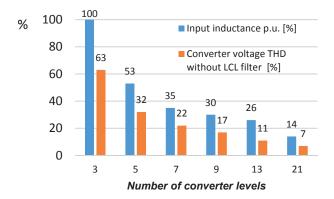

Fig. 16. The impact of converter voltage levels for the output voltage THD and input inductance

Possible reduction of LC filter inductance at the same value of output voltage THD (5%) for all discussed cascaded converters is shown in Fig. 16. The 21-level cascade converter can provide around 7 times lower inductance than the 3-level converter and around 4 times lower inductance than the 5-level converter.

### 5. Conclusions

The current research on converters for power distribution systems focuses mainly on cascaded multilevel converters, which are able to minimize or almost eliminate output passive filters, as well as provide higher reliability through possible converter

reconfiguration. This new trend of multilevel converters follows the direction of medium-voltage and high-voltage (above 20 kV) grid-side converters. Thanks to this, the reliability is improved, and the expensive and bulky transformer connecting RES to the grid can be eliminated.

However, there are still some aspects that require further development and research. An important issue that has to be addressed is efficiency improvement in terms of conduction losses caused by series connection of several semiconductors and high output currents. In order to reduce those losses, new advances in the semiconductor technology are still expected.

To reach higher voltage levels is a challenge for semiconductor technology, increasing not only the blocking voltage but other related technologies like isolation, gate drivers and sensors.

The further development requires research on fault management, intelligent modularization, and the possibility of reconfiguration on the fly [34, 45–46].

**Acknowledgments**. This work was supported by the TEAM-TECH/2016–1/5 project carried out within the TEAM-TECH program of the Foundation for Polish Science, co-financed by the European Union under the European Regional Development Fund.

#### REFERENCES

- [1] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L.G. Franquelo, B. Wu, J. Rodriguez, M. Perez, and J.I. Leon, "Recent advances and industrial applications of multilevel converters", *IEEE Transactions on Industrial Electronics* 57 (8), 2553–2580 (2010).

- [2] R. Teichmann, M. Malinowski, and S. Bernet, "Evaluation of three-level rectifiers for low voltage utility applications" *IEEE Transactions on Industrial Electronics* 52 (2), 471–482 (2005).

- [3] Ingeteam [online], available: www.ingeteam.com.

- [4] Converteam [online], available: www.converteam.com.

- [5] ABB [online], available: www.abb.com.

- [6] SIEMENS [online], available: www.siemens.com.

- [7] J. Meili, S. Ponnaluri, L. Serpa, P.K. Steimer, and J.W. Kolar, "Optimized pulse patterns for the 5-level ANPC converter for high speed high power applications", *Proc. 32nd IEEE IECON*, 2587–2592 (2006).

- [8] L.A. Serpa, P.M. Barbosa, P.K. Steimer, and J.W. Kolar, "Fivelevel virtual-flux direct power control for the active neutral-point clamped multilevel inverter", *Proc. IEEE Power Elec*tron. Spec. Conf., 1668–1674 (2008).

- [9] F. Kieferndorf, M. Basler, L. A. Serpa, J.-H. Fabian, A. Coccia, and G.A. Scheuer, "A new medium voltage drive system based on anpc-51 technology", *Proc. IEEE-ICIT*, Viña del Mar, 605– 611 (2010).

- [10] M. Sztykiel, R. Teodorescu, S. Munk-Nielsen, P. Rodriguez, L. Helle, and C. Busca, "Topology and technology survey on medium voltage power converters for large wind turbines", *International 10th Wind Integration Workshop*, Aarhus (2011).

- [11] G. Spagnuolo, G. Petrone, S.V. Araujo, C. Cecati, E. Friis-Madsen, E. Gubia, D. Hissel, M. Jasinski, W. Knapp, M. Liserre, P. Rodriguez, R. Teodorescu, and P. Zacharias, "Renewable energy operation and conversion schemes", *IEEE Industrial Electronics Magazine* 4 (1), 38–51, (2010).

- [12] M. Malinowski and S. Styński "Simulation of single-phase cascade multilevel PWM converters", *IEEE-Eurocon*, Warsaw, 1524–1529 (2007).

- [13] M. Malinowski, S. Styński, and M.P. Kaźmierkowski "Singlephase cascade multilevel PWM converter based on FLC modules with LC output sine filter" *IEEE-ISIE*, Cambridge, (2008).

- [14] P. Wiatr and M.P. Kaźmierkowski; "Model predictive control of multilevel cascaded converter with boosting capability – a simulation study", *Bull. Pol. Ac.: Tech.* 64 (3), 581–590 (2016).

- [15] M. Zygmanowski, B. Grzesik, M. Fulczyk, and R. Nalepa; "Selected aspects of Modular Multilevel Converter operation" *Bull. Pol. Ac.: Tech.* 62 (2), 375–385 (2014).

- [16] C. Rech and J. R. Pinheiro, "Hybrid multilevel converters: Unified analysis and design considerations", *IEEE Trans. On Industrial Electronics* 54 (2), 1092–2004 (2007).

- [17] W. McMurray, "Fast response stepped-wave switching power converter circuit", U.S. Patent 3 581 212, May 25, 1971.

- [18] J.A. Dickerson and G.H. Ottaway, "Transformerless power supply with line to load isolation", U.S. Patent 3 596 369, Aug. 3, 1971.

- [19] R.H. Baker, "High-voltage converter circuit", U.S. Patent 4 203 151, May 13, 1980.

- [20] O.M. Mueller and J.N. Park, "Quasi-linear IGBT inverter topologies", Proc. 9th Annu. APEC, 253–259 (1994).

- [21] A. Rufer, M. Veenstra, and K. Gopakumar, "Asymmetric multilevel converter for high resolution voltage phasor generation", *Proc. EPE*, p. 10 (1999).

- [22] J. Dixon, A.A. Breton, F.E. Rios, J. Rodriguez, J. Pontt, and M.A. Perez, "High-power machine drive, using nonredundant 27-level inverters and active front end rectifiers", *IEEE Trans. Power Electron.* 22 (6), 2527–2533 (2007).

- [23] S. Vazquez Perez, "Design of advanced control strategies and modulation techniques for cascaded H-bridge single-phase power converters", PhD Thesis, University of Seville, Seville, 2010.

- [24] D. Kai, Z. Yunping, and L. Lei, "Novel hybrid cascade asymmetric inverter based on 5-level asymmetric inverter", *PESC* '2005, Recife, 2302–2306 (2005).

- [25] A. Abu Sneineh and M.-Y. Wang, "Spectral analysis of hybrid capacitor-clamp cascade 13-level inverter", *ICIT'2006*, Mumbai, 271–276 (2006).

- [26] M. Carpaneto, M. Marchesoni, and L. Vaccaro, "A new cascaded multilevel converter based on NPC cells", *IEEE International Symposium on Industrial Electronics*, Vigo, 1033–1038 (2007).

- [27] S.A. Gonzales, M.I. Valla, and C.F. Christiansen, "Analysis of a cascade asymmetric topology for multilevel converters", *IEEE International Symposium on Industrial Electronics*, Vigo, 1027–1032 (2007).

- [28] P. Lezana and J. Rodriquez, "Mixed multicell cascaded multilevel inverter", *IEEE International Symposium on Industrial Electronics*, Vigo, Spain, 509–514 (2007).

- [29] Z. Wu, Y. Zou, and K. Ding, "Spectral analysis of novel hybrid modulated asymmetric 5-level inverter", *IEEE International Conference on Electric Machines and Drives*, 1647–1652 (2005).

- [30] M.D. Manjrekar, P.K. Steimer, and T. A. Lipo, "Hybrid multi-level power conversion system: A competitive solution for high-power applications", *IEEE Trans. On Ind. Application* 36 (3), 834–841 (2000).

- [31] J. Salaet and Pereira, "Contributions to the use of rotating frame control and space vector modulation for multilevel diodeclamped single-phase AC-DC power converters", PhD Thesis, Universitat Politecnica de Catalunya, Barcelona, 2006.

- [32] J.I. Leon, R. Portillo, S. Vazquez, J.J. Padilla, L.G. Franquelo, and J.M. Carrasco, "Simple unified approach to develop a time-domain modulation strategy for single-phase multilevel converters", *IEEE Transactions on Industrial Electronics* 55 (9), 3239–3248 (2008).

- [33] J.I. Leon, S. Vazquez, S. Kouro, L.G. Franquelo, J.M. Carrasco, and J. Rodriguez, "Unidimensional modulation technique for cascaded multilevel converters", *IEEE Transactions on Indus*trial Electronics 56 (8), 2981–2986 (2009).

- [34] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. Perez, "A survey on cascaded multilevel inverters", *IEEE Transaction on Industrial Electronics* 57 (7), 2197–2206 (2010).

- [35] R. Marquardt, "Stromrichterschaltungen mit verteilten energiespeichern", German Patent DE10103031A1, Jan. 24, 2001.

- [36] A. Lesnicar and R. Marquardt, "A new modular voltage source inverter topology", *Proc. 10th EPE*, 1–10 (2003).

- [37] M. Glinka, "Prototype of multiphase modular-multilevel-converter with 2 MW power rating and 17-level-output-voltage", Proc. IEEE 35th Power Electron. Spec. Conf. 4, 2572–2576 (2004).

- [38] M. Glinka and R. Marquardt, "A new AC/AC multilevel converter family", *IEEE Trans. Ind. Electron.* 52 (3), 662–669 (2005).

- [39] B. Gemmell, J. Dorn, D. Retzmann, and D. Soerangr, "Prospects of multilevel VSC technologies for power transmission", *Proc. IEEE/PES T&D Conf. Expo.*, 1–16 (2008).

- [40] L. Wang, D. Zhang, Y. Wang, B. Wu, and H.S. Athab, "Power and voltage balance control of a novel three-phase solid-state transformer using multilevel cascaded H-bridge inverters for microgrid applications", *IEEE Trans. Power Electron.* 31 (4), 3289–3301 (2016).

- [41] X. She, A. Q. Huang, and R. Burgos, "Review of solid-state transformer technologies and their application in power distribution systems", *IEEE Trans. Emerg. Sel. Topics Power Electron*. 1 (3), 186–198 (2013).

- [42] R. Peña-Alzola, G. Gohil, L. Mathe, M. Liserre, and F. Blaabjerg, "Review of modular power converters solutions for smart transformer in distribution system", *Proc. IEEE Energy Con-version Congr. and Expo.*, Denver, 380–387 (2013).

- [43] J.W. Kolar and J.E. Huber, "Solid-state trans-formers key design challenges, applicability, and future concepts", 8th Int. Power Electron. and Motion Control Conf., Hefei (2016). Available: https://goo.gl/nkaSUo.

- [44] J. Wen and K.M. Smedley, "Synthesis of multilevel converters based on single- and/or three-phase converter building blocks", *IEEE Trans. Power Electron.* 23 (3), 1247–1256 (2008).

- [45] M. Rolak, H.S. Che, and M. Malinowski, "Modelling and fault-tolerant control of 5-phase induction machine", *Bull. Pol. Ac.: Tech.* 63 (4), 997–1006 (2015).

- [46] T. Orlowska-Kowalska and P. Sobanski, "Simple diagnostic technique of a single IGBT open-circuit faults for a SVM-VSI vector controlled induction motor drive", *Bull. Pol. Ac.: Tech.* 63 (1), 281–288 (2015).

- [47] P. Lezana and G. Ortiz, "Extended operation of cascade multicell converters under fault condition", *IEEE Trans. Ind. Electron.* 56 (7), 2697–2703 (2009).

- [48] S. Stynski, M. Malinowski, M. Sedlak, and D. Sobczuk, "Metody modulacji jednofazowych wielopoziomowych przekształtników MSI z kondensatorami o zmiennym potencjale", *Przegląd Elektrotechniczny* 89 (4), 1–7 (2013).