BULLETIN OF THE POLISH ACADEMY OF SCIENCES TECHNICAL SCIENCES, Vol. 69(1), 2021, Article number: e136043

## DOI: 10.24425/bpasts.2021.136043

## A novel quasi-resonant ZVS boost converter with tapped inductor

Jakub DAWIDZIUK and Michał HARASIMCZUK to and Michał HARASIMCZUK

Abstract. The purpose of this paper is to propose a model of a novel quasi-resonant boost converter with a tapped inductor. This converter combines the advantages of zero voltage quasi-resonant techniques and different conduction modes with the possibility of obtaining a high voltage conversion ratio by using a tapped inductor, which results in high converter efficiency and soft switching in the whole output power range. The paper contains an analysis of converter operation, a determination of voltage conversion ratio and the maximum voltage across power semiconductor switches as well as a discussion of control methods in discontinuous, critical, and continuous conduction modes. In order to verify the novelty of the proposed converter, a laboratory prototype of 300 W power was built. The highest efficiency  $\eta = 94.7\%$  was measured with the output power  $P_0 = 260$  W and the input voltage  $V_{in} = 50$  V. The lowest efficiency of 90.7% was obtained for the input voltage  $V_{\rm in}=30~{

m V}$  and the output power  $P_{\rm o}=75~{

m W}$ . The model was tested at input voltages (30–50) V, output voltage 380 V and maximum switching frequency 100 kHz.

Key words: tapped inductor; boost converter; DC/DC converter; zero voltage switching.

#### 1. Introduction

Switched-mode power supplies (SMPSs) are widely used in industrial, medical, residential, and aerospace environments. Moreover, an interest in DC-DC converters, especially voltage boosting techniques, is constantly growing [1]. Modern SMPSs nowadays are dominated by a trend to achieve high efficiency, high power density and in many cases, they use a DC-DC converter with a high voltage conversion ratio. This is due to the fact that the full utilization of renewable sources requires a converting stage to match the demanded voltage for effective grid connection. One option to reduce the size of storage energy elements is to increase the converter switching frequency. However, in hard switching converters the increase in the switching frequency results in increased switching losses. The use of soft switching techniques reduces switching losses, increases efficiency, and reduces EMI.

Compared to conventional PWM converters, the converters with tapped-inductor configurations permit the duty cycle to be adjusted to the values which are neither close to 0 nor 1. Furthermore, a better utilization of switching and passive components can be achieved. The coupled inductor techniques provide solutions to achieve a high voltage conversion ratio, a low voltage stress on the active switch, and high efficiency without the penalty of high duty ratio [2–4]. Furthermore, utilizing a coupled inductor to boost the voltage makes leakage inductance reduce recovery problem by limits di/dt of the out-

Manuscript submitted 2020-06-16, revised 2020-10-06, initially accepted for publication 2020-10-30, published in February 2021

put diode. Simultaneously, in a boost converter with a coupled inductor when the transistor is turned off, leakage inductance leads to voltage spikes across the switches [5], which increases energy losses and EMI. In such topologies clamp circuits are required.

To solve the problem of increasing switching losses as the frequency increases, soft switching techniques should be used. The zero-voltage switching (ZVS), and the zero-current switching (ZCS) techniques are two commonly used soft switching methods. By adopting these techniques, either the voltage or the current is zero during the switching transitions, which largely reduces the switching losses and also increases the reliability of power supplies.

Quasi-resonant converters (QRCs) were introduced in [6–8] to overcome the disadvantage of PWM converters operating at a high switching frequency. In QRCs, switches can be turned on at a zero voltage or turned off at a zero current so that the switching losses are zero and the switching frequency could be high. However, the switches in QRCs have to withstand the high voltage or the current stress. These techniques are used in low power applications.

In active clamp flyback converters, the leakage energy is recovered, and voltage ratings of semiconductors are reduced [9, 10]. In those converters, the soft-switching technique could be used with leakage inductance or an additional inductor. However, the implementation of this technique reduces the effective duty cycle; hence, a coupled inductor with higher turns ratio is required.

High efficiency and soft switching are achieved in zero voltage/current transition [11, 12] and resonant switched capacitor [13] techniques. However, in such a circuit the converter is complex and needs additional components.

<sup>&</sup>lt;sup>1</sup> Department of Automatic Control and Robotics, Bialystok University of Technology, ul. Wiejska 45D, 15-351 Bialystok, Poland

<sup>&</sup>lt;sup>2</sup>Department of Electrical Engineering, Power Electronics and Electrical Power Engineering, Bialystok University of Technology, ul. Wiejska 45D, 15-351 Bialystok, Poland

<sup>\*</sup>e-mail: m.harasimczuk@pb.edu.pl

The article proposes a new type of quasi-resonant ZVS boost converter with a tapped inductor and an active-edge resonant cell (AERC), which develops the family of novel topologies described in [8, 14, 15].

## 2. Two-Transistor Tapped-Inductor ZVS Quasi-Resonant Boost Converter

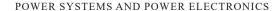

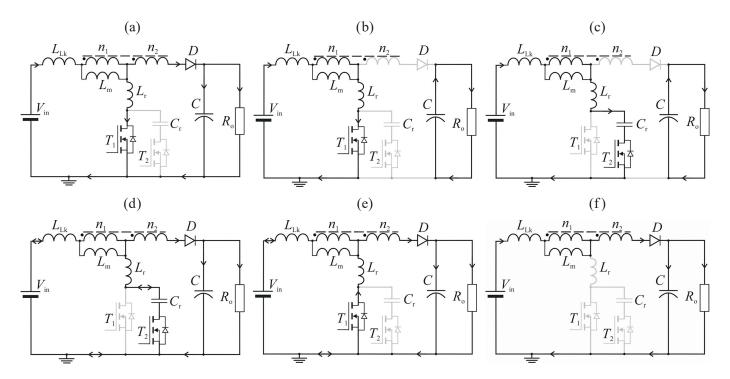

Figure 1 shows a single switch quasi-resonant converter with a tapped inductor [8]. In this circuit, the transistor is soft switched over a narrow range of output power. The maximum output power is limited by the output resistance, which increases the voltage  $V_{\rm DS}$  across the transistor T.

Fig. 1. Simplified converter scheme presented in [8]

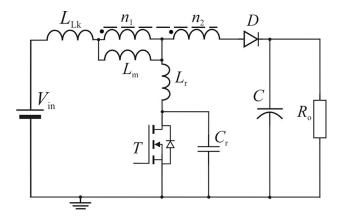

In order to improve the technical parameters, a two-transistor tapped-inductor ZVS-AERC boost converter is proposed, shown in Fig. 2. The addition of the transistor  $T_2$  enables us to achieve higher efficiency and soft switching in a wider range of output power. Tapped inductors provide a high voltage ratio and high efficiency. The two windings,  $n_1$  and  $n_2$ , of the tapped inductor are on the same core and magnetically coupled. Tapping the inductor is beneficial because it optimizes the duty cycle of the converter to achieve the maximum efficiency.

Fig. 2. Simplified circuit scheme of the proposed converter

Tapping the inductor also allows for reducing voltage and current ratings of semiconductors power elements. The leakage inductance  $L_{\rm Lk}$  of the coupled inductor with the resonant inductance  $L_{\rm r}$  form equivalent inductance of the resonant circuit  $L_{\rm eq}$  described by the equation:

$$L_{\rm eq} = L_{\rm r} + L_{\rm Lk} \left(\frac{N}{N+1}\right)^2,\tag{1}$$

where  $N = n_2/n_1$  is the turns ratio of the tapped inductor;  $n_1$  is the turns of primary winding and  $n_2$  is the turns of secondary winding.

The equivalent inductance  $L_{\rm eq}$  together with the capacitor  $C_{\rm r}$  forms a resonant circuit. The resonant circuit can be implemented without an additional resonant inductor, which is the main advantage compared to the circuit presented in [14]. Additionally, in the ZVS converter reverse recovery problems caused by transistors body diodes are reduced.

In the presented converter, the transistors are controlled with a variable frequency and a constant value of the current, at which the transistor  $T_1$  is turned off, thus making the maximum voltage values on the switches independent of load changes. This facilitates the use of transistors with a lower resistance  $R_{\rm DS(on)}$ , which reduces conduction losses and increases efficiency. The losses in the transistor  $T_2$  are much lower than in the transistor  $T_1$  due to the short conduction time of switch  $T_2$ . Moreover, as a result of lowering the relative frequency  $f_{\rm s}/f_{\rm r}$ , the capacitor rms current and the equivalent inductance were reduced.

The additional transistor  $T_2$ , connected in a series with the capacitor  $C_r$ , initiates a soft switching (ZVS) of the transistor  $T_1$ . Turning on the  $T_2$  transistor enables parallel to the transistor  $T_1$  discharged resonant capacitor  $C_r$  and allows us to turn off the transistor  $T_1$  at zero voltage.

In CCM, the transistor  $T_1$  is turned on at zero current and turned off at zero voltage, in DCM both transistors are switched at zero voltage. The voltage conversion ratio  $k_v$  is determined by the duty cycle D of the transistor  $T_1$ . The resonant operation of the converter facilitates the elimination of the negative impact of leakage inductance on voltage spikes, efficiency, and EMI emission.

In order to explain the principle of operation of this converter, it is analyzed in steady-state and different conduction modes: the critical conduction mode (CRM), the continuous conduction mode (CCM) and the discontinuous conduction mode (DCM).

Experimental results and waveforms at 300 W illustrate the performances of the proposed Two-Transistor Tapped-Inductor ZVS-AERC Boost Converter.

#### 3. Principle of operation

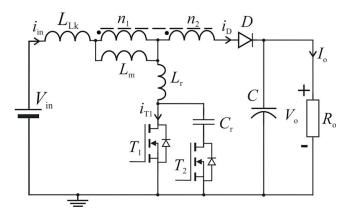

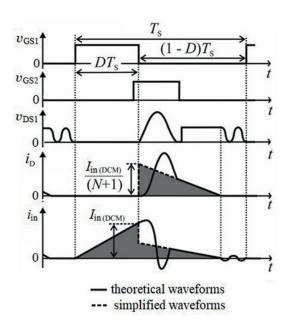

Key waveforms are shown in Fig. 3. The circuit operation can be divided into six modes (intervals), whose equivalent circuits are shown in Fig. 4. They are described as follows:

Fig. 3. Key waveforms of the proposed converter

**Interval 1**  $(t_1 - t_2)$  **Fig. 4a.** Before this interval, the switches  $T_1$ ,  $T_2$  are off, the output diode D is forward biased. The energy from source  $V_{\rm in}$  and the energy accumulated in the tapped inductor are transferred to the load. At  $t_1$  the transistor  $T_1$  is turned on – the transistor current increases and the output diode D current

decreases. The transistor current  $i_{\rm T1}$  increases linearly; the slope of that current is limited by the equivalent inductance  $L_{\rm eq}$ . This facilitates turning on the transistor at zero current and reducing the reverse recovery current of the output diode. In this mode the voltage on equivalent inductance is given by:

$$\upsilon_{\text{eq}}(t - t_1) = \frac{V_{\text{o}} + NV_{\text{in}}}{N + 1}.$$

(2)

The interval  $t_1 - t_2$  can be defined as:

$$t_2 - t_1 = \frac{L_{\text{eq}} I_{\text{in}}(N+1)}{V_0 + N V_{\text{in}}}.$$

(3)

**Interval 2**  $(t_2 - t_3)$  **Fig. 4b.** In this interval the transistor  $T_1$  remains switched on, and the diode D is reverse biased. The energy from the voltage source  $V_{\rm in}$  is accumulated in the tapped inductor. In this interval, the transistor  $T_2$  is switched on at zero current and zero voltage. This interval is given by:

$$t_3 - t_2 = DT_s - (t_2 - t_1), \tag{4}$$

where D is the duty cycle of the transistor  $T_1$ .

**Interval 3**  $(t_3 - t_4)$  **Fig. 4c.** At  $t_3$  the transistor  $T_1$  is turned off at zero voltage. In this interval, the capacitor  $C_r$  is charged with a constant current  $I_{\rm in}$  to the level at which the diode D is forward biased. The voltage on capacitor  $C_r$  and the interval  $t_3 - t_4$  can be described by the following equations:

$$\nu_{\rm Cr}(t_4) = \frac{V_{\rm o} + NV_{\rm in}}{N+1},$$

(5)

Fig. 4. Equivalent diagrams of the converter in six characteristic intervals

$$t_4 - t_3 = \frac{C_{\rm r} \nu_{\rm Cr}(t_4)}{I_{\rm in}} = \frac{C_{\rm r}(V_{\rm o} + NV_{\rm in})}{I_{\rm in}(N+1)}.$$

(6)

**Interval 4**  $(t_4 - t_5)$  **Fig. 4d.** In this interval inductance  $L_{\rm eq}$  and capacitor  $C_{\rm r}$  resonate. The principal equations describing voltages and currents in this interval can be defined as follows:

$$i_{\rm Cr}(t - t_4) = i_{\rm Lr}(t - t_4) = I_{\rm in} \cos[\omega_{\rm r}(t - t_4)],$$

(7)

$$i_{\rm D}(t-t_4) = \frac{I_{\rm in}}{N+1} \left\{ 1 - \cos\left[\omega_{\rm r}(t-t_4)\right] \right\},$$

(8)

$$i_{\rm in}(t-t_4) = \frac{I_{\rm in}\{N\cos[\omega_{\rm r}(t-t_4)]+1\}}{N+1},$$

(9)

$$\psi = \frac{\upsilon_{\rm Cr}(t_4)}{I_{\rm in}Z} = \frac{V_{\rm o} + NV_{\rm in}}{I_{\rm in}Z(N+1)},$$

(10)

$$t_5 - t_4 = \frac{\pi + \arcsin(\psi)}{I_{in}(N+1)},$$

(11)

where  $\Psi$  specifies the soft switching condition;  $Z=(L_{\rm eq}/C_{\rm r})^{1/2}$ ;  $\omega_{\rm r}=1/(L_{\rm eq}C_{\rm r})^{1/2}$ .

To achieve the soft switching of transistors the following inequality must be satisfied:

$$\frac{V_{\rm o} + NV_{\rm in}}{N+1} \le I_{\rm in}Z \Rightarrow \psi \le 1. \tag{12}$$

**Interval 5**  $(t_5 - t_6)$  **Fig. 4e.** In this interval the body diode of the transistor  $T_1$  is conducting. The negative current  $i_{T1}$  of the transistor  $T_1$  increases to zero. The output diode current  $i_D$  decreases, and the input current  $i_{in}$  increases to the same value  $I_{in}/(N+1)$ . The capacitor  $C_r$  remains discharged, allowing the transistor  $T_2$  to turn off at zero voltage. The inductor current at  $t_5$  may be described by the following equation:

$$i_{\rm Lr}(t_5) = -I_{\rm in}\sqrt{1-\psi^2}$$

(13)

The duration of this interval depends on current  $i_{Lr}(t_5)$  equivalent inductance and constant voltage on that inductance during the analyzed interval:

$$t_6 - t_5 = \frac{L_{\text{eq}} i_{\text{Lr}}(t_5)}{v_{\text{Cr}}(t_4)} = \frac{L_{\text{eq}}(N+1) I_{\text{in}} \sqrt{1 - \psi^2}}{V_0 + N V_{\text{in}}}.$$

(14)

Considering Eqs. (7–11), the diode current and the input current at  $t_5$  are given by:

$$i_{\rm D}(t_5) = \frac{I_{\rm in}(1+\sqrt{1-\psi^2})}{N+1},$$

(15)

$$i_{\rm in}(t_5) = \frac{I_{\rm in}(1 - N\sqrt{1 - \psi^2})}{N + 1}.$$

(16)

**Interval 6** ( $t_6 - t_7$ ) **Fig. 4f.** In this interval, both transistors are turned off, and the diode D is forward biased. The energy from the voltage source  $V_{\rm in}$  and the tapped inductor is transferred to the load. The duration of the interval depends on the transistor  $T_1$  turn-off time according to the equation:

$$t_7 - t_6 = T_s(1-D) - (t_4 - t_3) - (t_5 - t_4) - (t_6 - t_5),$$

(17)

where  $T_s(1-D)$  is the transistor  $T_1$  turn-off time.

## 4. Voltage conversion ratio

The voltage conversion ratio was determined by comparing the converter input power with the output power:

$$V_{\rm in}I_{\rm in(av)} = V_{\rm o}I_{\rm o}, \ k_{\rm u} = \frac{V_{\rm o}}{V_{\rm i}} \Rightarrow k_{\rm u} = \frac{I_{\rm in(av)}}{I_{\rm o}}.$$

(18)

The average input current was determined on the basis of Eqs. (1-18) and described by the following equation:

$$I_{in(av)} = \frac{1}{T_S} \begin{pmatrix} I_{in} \left( T_s D - \frac{N}{2(N+1)} (t_2 - t_1) + (t_4 - t_3) \right) + \\ + \frac{I_{in}}{N+1} \left( \int_{t_4}^{t_5} \left( N \cos(\omega_r t) + 1 \right) dt \right) + \\ + \frac{i_{in}(t_5)(t_6 - t_5)}{2} + \frac{I_{in}}{N+1} (t_7 - t_6) \end{pmatrix}, (19)$$

$$I_{\text{in(av)}} = I_{\text{in}} \left( \frac{DN+1}{N+1} - \frac{N(2-\psi^2)}{4\pi\psi(N+1)} \frac{f_s}{f_r} \right).$$

(20)

The output current  $I_0$  is equal to the average current of the diode D, according to the following equations:

$$I_{o} = \begin{pmatrix} \frac{I_{in}}{N+1} \int_{t_{4}}^{t_{5}} (1 - \cos(\omega_{r}t)) dt + \\ + (i_{D}(t_{5}) + \frac{I_{in}}{N+1}) \frac{(t_{6} - t_{5})}{2} + \\ + I_{in} \frac{(t_{7} - t_{6}) + (t_{2} - t_{1})/2}{N+1} \end{pmatrix}$$

(21)

$$I_{\rm o} = \frac{I_{\rm in} \left( 1 - D + \frac{2 - \psi^2}{4\pi\psi} \frac{f_{\rm s}}{f_{\rm r}} \right)}{N + 1}.$$

(22)

With regard to Eqs. (18–22), the voltage conversion ratio is given by:

$$k_{v} = \frac{ND + 1 - N\frac{2 - \psi^{2}}{4\pi\psi}\frac{f_{s}}{f_{r}}}{1 - D + \frac{2 - \psi^{2}}{4\pi\psi}\frac{f_{s}}{f_{r}}} \approx \frac{ND + 1}{1 - D}.$$

(23)

# 5. Control and analysis of converter operating modes

Usually, in resonant converter soft switching region and voltage ratings of semiconductors depend on output resistance and characteristic impedance. In the proposed converter utilization different control methods depending on output resistance facilitate obtaining soft switching in a wide power range and constant voltages on switches.

This section presents a discussion on the control method of the converter in three conduction modes. If the resonant frequency  $f_r$  is significantly higher than the control frequency  $f_s$ , it may be assumed that  $i_{\rm in}(t_3)=i_{\rm in}(t_4)=i_{\rm in}(t_5)+Ni_{\rm D}(t_5)=I_{\rm in(max)}$ . The idea behind the proposed control method relies on turning off the main transistor  $T_1$  at a constant current described by the following equation:

$$I_{\text{in(max)}} = \frac{V_{\text{o}} + NV_{\text{in}}}{Z(N+1)} = > \psi = 1,$$

(24)

which ensures a constant voltage on the capacitor  $C_{\rm r}$  (constant voltage on  $v_{\rm DS1}$ ), independent of output resistance.

**5.1.** Critical conduction mode. The critical conduction mode occurs when the main transistor  $T_1$  turns on and the tapped inductor current reaches zero. The maximum current of the transistor in that mode can be given by:

$$I_{\text{in(CRM)}} = \frac{(V_{\text{o}} - V_{\text{in}})(1 - D)T_{\text{s}}}{L_{\text{m}}(N+1)},$$

(25)

In that mode the transistors are switched with a fixed frequency described by:

$$f_{\rm s(CRM)} = \frac{R_{\rm o}(k_{\rm o} - 1)}{2L_{\rm m}k_{\rm o}(N + k_{\rm o})^2} \,. \tag{26}$$

On the basis on Eq. (24), in order to ensure the soft switching of transistors, the value of characteristic impedance should be in accordance with the equation:

$$Z = \frac{R_{\rm o}}{2k_{\rm D}(N+1)} \,. \tag{27}$$

**5.2. Continuous conduction mode.** In this mode, the transistors are switched at a frequency higher than the frequency described by Eq. (26). The maximum input current in this mode can be given by:

$$I_{\rm in(CCM)} = \frac{I_{\rm o}(N+1)}{1-D} + \frac{(V_{\rm o} - V_{\rm in})(1-D)T_{\rm s}}{2L_{\rm m}(N+1)} \ . \tag{28}$$

Assuming that  $i_{\rm in}(t_3) = i_{\rm in}(t_4) = i_{\rm in}(t_5) + Ni_{\rm D}(t_5) = I_{\rm in(CCM)}$ , and using Eq. (24), the operating frequency of the analyzed converter in CCM is given by:

$$f_{\text{s(CCM)}} = \frac{R_{\text{o}}Z(N+1)(k_{\text{v}}-1)}{2L_{\text{m}}(N+k_{\text{v}})^{2}\left[R_{\text{o}}-k_{\text{v}}Z(N+1)\right]}.$$

(29)

In order to ensure the soft switching of transistors, the value of characteristic impedance is given by:

$$Z \le \frac{2L_{\rm m}R_{\rm o}f_{\rm s}(N+k_{\rm o})^2}{(N+1)\left[2L_{\rm m}f_{\rm s}k_{\rm o}(N+k_{\rm o})^2 + R_{\rm o}(k_{\rm o}-1)\right]}.$$

(30)

**5.3. Discontinuous conduction mode.** In the discontinuous conduction mode, the transistors are switched at a frequency lower than the frequency described by Eq. (26). Unlike CRM and CCM, the voltage conversion ratio is not described by Eq. (23). To calculate it, the input power was compared with the output power of the converter in accordance with the following equations:

$$I_{\text{in(av)}} = \frac{1}{T_{\text{S}}} \frac{V_{\text{in}} D T_{\text{S}}}{2L_{\text{m}}} + I_{\text{o}},$$

(31)

$$P_{\rm in} = V_{\rm in} \left( \frac{DV_{\rm in}}{2L_{\rm m}} + I_{\rm o} \right), \tag{32}$$

$$P_{o} = V_{o}I_{o}, \tag{33}$$

$$k_{\rm v} = \sqrt{\frac{D^2 R_{\rm o}}{2L_{\rm m} f_{\rm s}} + \frac{1}{4}} + \frac{1}{2} \,.$$

(34)

In CRM, the soft switching of transistors can be achieved by maintaining the minimum turn on time of the transistor  $T_{1,}$  as follows:

$$DT_{\rm s} \ge \frac{L_{\rm m}I_{\rm in(DCM)}}{V_{\rm in}}.$$

(35)

On the basis on Eqs. (24) and (35) the switching frequency may be described by:

$$f_{\text{s(DCM)}} = \frac{2Z^2 k_{\text{v}} (N+1)^2 (k_{\text{v}} - 1)}{L_{\text{m}} R_{\text{o}} (N+k_{\text{v}})^2}.$$

(36)

In CCM, during switching on the transistor  $T_1$  the slope of the currents change in the transistor and the output diode are limited by the equivalent inductance. In DCM, the transistor is switched on when the D diode is not conducting, and this completely eliminates the diode reverse recovery problem. Moreover, in this mode the transistor  $T_1$  may be turned on at zero voltage. After the current in magnetizing inductance reaches zero, the output capacitance of transistors and magnetizing inductance resonate. The sinusoidal voltage  $V_{\rm DS1}$  enables us to turn on the transistor  $T_1$  at a voltage much lower than the input voltage (Fig. 5).

To obtain the minimum  $V_{\rm DS}$  voltage on transistor  $T_{\rm l}$ , it should be switched with certain frequency and duty cycle

Fig. 5. Theoretical and simplified waveforms of voltages and currents in DCM

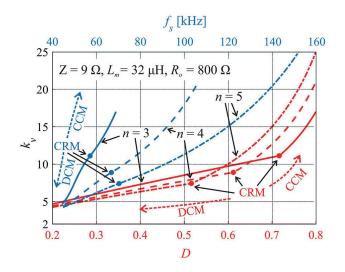

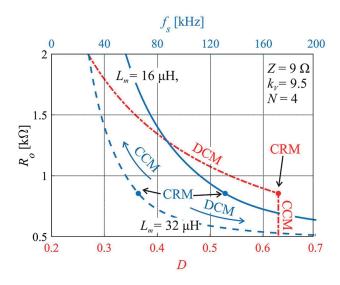

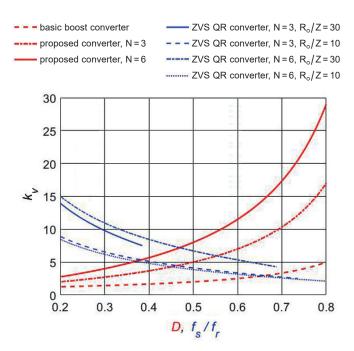

where  $\psi = 1$  (Eq. (24)). Voltage conversion ratio as a function of switching frequency  $f_s$  and duty cycle D for three different turn ratio n and  $\psi = 1$  with marked different conduction mode is presented on Fig. 6. In the converter,  $\psi$  may be less than one, which increases the maximum  $V_{\rm DS1}$  voltage. In this case switching frequency is lower than the frequency on Fig. 6. Figure 7 shows output resistance as a function of switching frequency and duty cycle for two different magnetizing inductance  $L_{\rm m}$ . Duty cycle curve is independent of the magnetizing inductance. In based on the characteristics presented on Fig. 7, it can be observed that the switching frequency depends on output resistance and magnetizing inductance.

In DCM duty cycle increases with increasing frequency (Eq. (34)), in CCM duty cycle is constant (Eq. (23)). A slight

Fig. 6. Voltage conversion ratio as a function of switching frequency and duty cycle of the proposed converter for  $\psi = 1$

Fig. 7. Load resistance  $R_{\rm o}$  as a function of switching frequency and duty cycle for  $\psi=1$

increase the output power in CCM forces a high frequency increase. Theoretical maximum output power of the converter is doubled than the output power in CRM mode (for  $\psi = 1$ ).

## 6. Voltage and current stress of power devices

The maximum voltage  $v_{\rm DS1}$  on transistor  $T_1$  occurs in the interval  $t_4 - t_5$ . Assuming that the transistor is switched at a frequency determined by Eq. (24), the maximum voltage is given by:

$$V_{\rm DS1(max)} = \frac{2(V_{\rm o} + NV_{\rm in})}{N+1} \,. \tag{37}$$

The maximum voltage  $v_{\rm DS2}$  on the transistor  $T_2$  occurs in the interval  $t_6-t_7$  and is determined by:

$$V_{\rm DS2(max)} = \frac{V_{\rm o} + NV_{\rm in}}{N+1} \,.$$

(38)

Similarly, the maximum voltage across the diode *D* occurs in the same interval, and it can be calculated in accordance with the following equation:

$$V_{\rm D(max)} = V_{\rm o} + NV_{\rm in}. \tag{39}$$

In order to calculate current stress of the converter components, a constant current in magnetizing inductance in interval  $(t_3-t_6)$ , and fixed duration of intervals  $(t_4-t_3)=1/\omega_{\rm r}$ ,  $(t_5-t_4)=3/(4f_{\rm r})$  were assumed. Derivations include the effect of current ripple in magnetizing inductance in intervals  $(t_2-t_3)$  and  $(t_6-t_7)$ . Interval  $(t_1-t_2)$  was omitted. Parameter A (44) was defined to simplified RMS current descriptions. RMS currents were calculated for DCM and CCM accordance with Eqs. (40–48).

$$I_{\text{D(RMS, CCM)}} = \frac{I_{\text{o}}}{N+1} \sqrt{\left( \left[ N + k_{v} \right]^{2} + \frac{A^{2}}{3} \right) \left( \frac{N+1}{N+k_{v}} - \frac{f_{\text{s}}}{f_{\text{r}}} \frac{3\pi+2}{4\pi} \right) + \frac{f_{\text{s}}}{f_{\text{r}}} \left( A + N + k_{v} \right)^{2} \left( \frac{1}{\pi} + \frac{9}{8} \right)}, \tag{40}$$

$$I_{\text{in(RMS, CCM)}} = \frac{I_{\text{o}}}{N+1} \sqrt{\left( \left[ N + k_{v} \right]^{2} + \frac{A^{2}}{3} \right) \left( \frac{\left[ N+1 \right]^{2} \left[ k_{v}-1 \right] + N+1}{N+k_{v}} - \frac{f_{\text{s}}}{f_{\text{r}}} \frac{3\pi+2}{4\pi} \right) + \frac{f_{\text{s}}}{f_{\text{r}}} (A+N+k_{v})^{2} \left( \frac{N^{2}+1}{2\pi} + \frac{3N^{2}}{4} + \frac{3}{4} \right)}, \quad (41)$$

$$I_{\text{D(RMS, DCM)}} = \frac{I_{\text{o}}}{N+1} \sqrt{\frac{R_o(k_v - 1)}{L_m k_v} \left(\frac{2\sqrt{2}[N+1]}{3} \sqrt{\frac{L_m k_v}{R_o f_{\text{s}}(k_v - 1)}} + \frac{1}{f_{\text{r}}} \left[\frac{5}{3\pi} + \frac{7}{4}\right]\right)},$$

(42)

$$I_{\text{in(RMS, DCM)}} = \frac{I_{\text{o}}}{N+1} \sqrt{\frac{R_{\text{o}}(k_{\text{v}}-1)}{L_{\text{m}}k_{\text{v}}} \left(\frac{2}{3} \left[\frac{1}{\{N+1\}\{k_{\text{v}}-1\}}+1\right] \sqrt{\frac{2L_{\text{m}}k_{\text{v}}(k_{\text{v}}-1)}{R_{\text{o}}f_{\text{s}}}}\right) + \frac{1}{4(N+1)^{2}f_{\text{r}}} \left(\frac{4N^{2}}{\pi} + \frac{8}{3\pi} + 3N^{2} + 4\right)}, (43)$$

$$A = \frac{R_o(k_v - 1)}{2L_{\text{to}} f_v k_v(k_v + N)}, \qquad (44) \quad I_{\text{in(max)}} = I_{\text{in}} + \frac{\Delta I_{\text{Lm}}}{2} = I_o \left( N + \frac{k_v}{n} \right) + \frac{\Delta I_{\text{Lm}}}{2} = 15.4 \text{ A.} \quad (50)$$

$$I_{\text{T1(RMS, CCM)}} = I_{\text{o}} \sqrt{(k_{\nu} - 1) \left(\frac{A^2}{3(N + k_{\nu})} + N + k_{\nu}\right)},$$

(45)

$$I_{\text{T2(RMS, CCM)}} = I_{\text{o}} \left( A + N + k_{v} \right) \sqrt{\frac{f_{\text{s}}}{f_{\text{r}}} \left( \frac{1}{2\pi} + \frac{3}{8} \right)},$$

(46)

$$I_{\text{T1(RMS, DCM)}} = \frac{I_o}{\sqrt{3}} \sqrt[4]{\frac{8R_o(k_v - 1)^3}{L_{\text{m}} f_{\text{s}} k_v}}},$$

(47)

$$I_{\text{T2(RMS, DCM)}} = \frac{I_o}{2} \sqrt{\frac{R_o(k_v - 1)(3\pi + 4)}{\pi L_m f_t k_v}} \ . \tag{48}$$

## 7. Laboratory model design and experimental results

The converter was subject to experimental tests. The ultimate goal of the design laboratory model is to achieve high efficiency and high-power density while reaching the voltage conversion ratio requirement for all load conditions. Equation (23)was used to calculate the turns ratio N to achieve the required voltage conversion ratio of approximately 7.6 at the duty ratio D=0.6. Another important parameter is magnetizing inductance because of the ripple of the current effects on turn-off conditions of the transistor  $T_2$ . Using the simplified current waveform in Fig. 5, the current ripple in the magnetizing inductance and the maximum input current value for data  $V_{\rm in}=50$  V,  $k_{\rm v}=7.6$ ,  $\eta=0.9$ ,  $f_{\rm s}=100$  kHz,  $I_{\rm o}=V_{\rm o}/R_{\rm o(min)}$ ,  $R_{\rm o(min)}=480$   $\Omega$  were calculated based on Eq. (23) as follows:

$$\frac{\Delta I_{\rm Lm}}{2} = \frac{V_{\rm in}DT_s}{2L_{\rm m}} = \frac{V_{\rm in}(k_{\rm v}/\eta - 1)}{2L_{\rm m}(N + k_{\rm v}/\eta)f_s} = 5.5 \,\mathrm{A}\,,\tag{49}$$

The parameters of the resonant circuit were calculated based on Eq. (30) for the maximum output power  $P_{\rm o}=300$  W, the maximum transistor switching frequency  $f_{\rm s}=100$  kHz and input voltage  $V_{\rm in}=50$  V. In the laboratory model the resonant inductor was placed in series with the secondary winding of the tapped inductor and with leakage inductance forms equivalent inductance. The maximum voltages of switches were calculated using Eqs. (37–39). The specifications and parameters of the converter are provided in Table 1.

Table 1 List of power components and parameters of the laboratory model of the converter

| Description                        | Values                          |

|------------------------------------|---------------------------------|

| Input voltage $V_{\rm in}$         | (30–50) V                       |

| Output voltage $V_{\rm o}$         | 380 V                           |

| Switching frequency $f_s$          | (25-100) kHz                    |

| Maximum output power $P_0$         | 300 W                           |

| Transistor $T_1$                   | IRFB4332 (250 V/29 m $\Omega$ ) |

| Transistor $T_2$                   | IRFB4228 (150 V/12 mΩ)          |

| Diode D                            | C4D05120A (1.4 V/1.2 kV)        |

| Resonant inductance $L_{\rm r}$    | 38 μH (core MS-130026)          |

| Resonant capacity $C_{\rm r}$      | 37.6 nF (ceramic COG)           |

| Equivalent inductance $L_{\rm eq}$ | 2.3 μΗ                          |

| Resonant frequency $f_{\rm r}$     | 515 kHz                         |

| Magnetizing inductance $L_{\rm m}$ | 27 μH (core MS-432115)          |

| Coupling coefficient k             | 0.97                            |

| Turns ratio $N = n_2/n_1$          | 53/13                           |

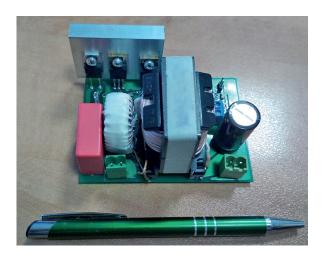

The Arnold Magnetic cores were used to build tapped (MS-432115) and resonant (MS-130026) inductors. The laboratory model with power density 1.06 kW/dm<sup>3</sup> and dimensions 93×66×46 mm of the proposed converter is shown in Fig. 8.

Fig. 8. Laboratory model of the proposed converter

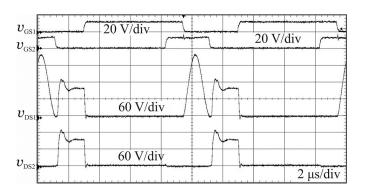

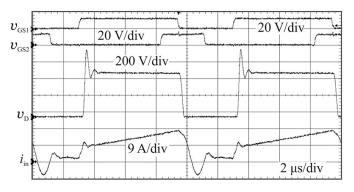

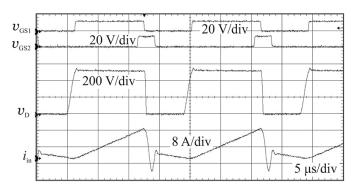

The efficiency of the converter was measured by the digital multimeter Brymen 857s, and the waveforms were measured by the digital oscilloscope Tektronix DPO5034. Tests were carried out in open loop system; transistors were switched by Cyclon II FPGA module. Figures 9–14 show experimental waveforms of the converter laboratory model for the input voltage  $V_{\rm in}=40~{\rm V}$  and the output voltage  $V_{\rm o}=380~{\rm V}$ . For the duty cycle  $D\approx0.6$ , the voltage and current waveforms are shown in Figs. 9, 10 at

Fig. 9. Transistors voltages  $V_{\rm GS1}$ ,  $V_{\rm GS2}$ ,  $V_{\rm DS1}$  and  $V_{\rm DS2}$  ( $P_{\rm o}=300$  W,  $f_{\rm s}=100$  kHz,  $R_{\rm o}=480$   $\Omega$ ,  $V_{\rm DS1(max)}=215$  V,  $V_{\rm DS2(max)}=125$  V)

Fig. 10. Transistors voltages  $V_{\rm GS1}$  and  $V_{\rm GS2}$ , diode voltage  $V_{\rm D}$  and input current  $i_{\rm in}$  ( $P_{\rm o}=300$  W,  $f_{\rm s}=100$  kHz,  $R_{\rm o}=480$   $\Omega$ ,  $V_{\rm D(max)}=800$  V,  $i_{\rm in(max)}=16.8$  A)

Fig. 11. Transistors voltages  $V_{\rm GS1}$ ,  $V_{\rm GS2}$ ,  $V_{\rm DS1}$  and  $V_{\rm DS2}$  ( $P_{\rm o}=183~{\rm W}$ ,  $f_{\rm s}=52~{\rm kHz}$ ,  $R_{\rm o}=790~\Omega$ ,  $V_{\rm DS1(max)}=215~{\rm V}$ ,  $V_{\rm DS2(max)}=120~{\rm V}$ )

Fig. 12. Transistors voltages  $V_{\rm GS1}$  and  $V_{\rm GS2}$ , diode voltage  $V_{\rm D}$  and input current  $i_{\rm in}$  ( $P_{\rm o}=183$  W,  $f_{\rm s}=52$  kHz,  $R_{\rm o}=790$   $\Omega$ ,  $V_{\rm D(max)}=520$  V,  $i_{\rm in(max)}=16$  A)

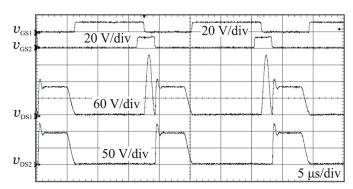

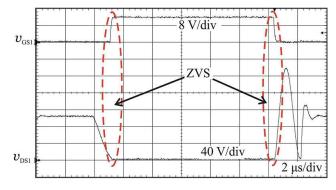

Fig. 13. Transistor  $T_1$  voltages  $V_{\rm GS1}$  and  $V_{\rm DS1}$  during turn-on and turn-off at zero voltage

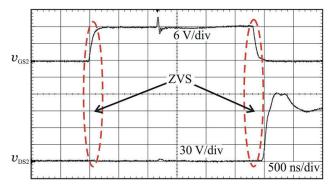

Fig. 14. Transistor  $T_2$  voltages  $V_{\rm GS2}$  and voltage  $V_{\rm DS2}$  during turn-on and turn-off at zero voltage

maximum output power  $P_0 = 300$  W, and in Figs. 11, 12 at the output power 183 W, at which the converter works in DCM. When the transistor  $T_2$  is turned off, there appears resonance between the equivalent inductance and the resonant capacitor (Figs. 9–11).

Figures 13, 14 illustrate the soft switching of the transistors  $T_1$  and  $T_2$ . Both transistors are turned on and off at zero voltage. To provide ZVS, the transistors must be turned off before changing the direction of the flowing current. In the case when the transistors are turned off, the current starts to flow through their forward biased body diodes.

To suppress spikes on transistors  $V_{\rm DS}$  voltages after turn-off transistor  $T_2$  and diode  $V_{\rm D}$  voltage after turn-on transistor  $T_1$ , parallel with those components were connected RC snubber circuits ( $C_{\rm SNUB(T1)} = 2.2~\rm nF$ ,  $R_{\rm SNUB(T1)} = 47~\Omega$ ,  $C_{\rm SNUB(D)} = 47~\rm pF$ ,  $R_{\rm SNUB(D)} = 1~\rm k\Omega$ ).

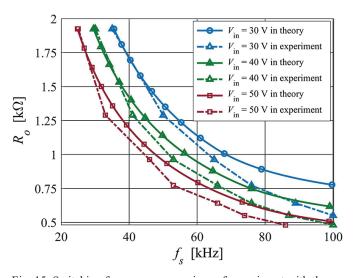

Figure 15 shows a switching frequency comparison of the experiment with theory. Theoretical curves were determined for Table 1 data in accordance with Eqs. (29) and (36). The curves obtained experimentally are similar to theoretical ones. The differences occur at high output power and high voltage gain. They result from the non-constant current in magnetizing inductance in interval  $t_3 - t_6$  (in theoretical derivations was assumed constant current in this interval) and the power losses in the converter.

Fig. 15. Switching frequency comparison of experiment with theory

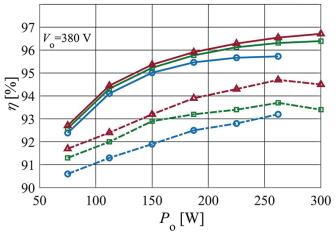

Figure 16 shows a comparison of the measured and theoretical efficiency of the proposed converter for the output voltage 380 V and the input voltages 30, 40, 50 V. The output load changed at a constant output voltage, thereby changing the output power, switching frequency and duty ratio while maintaining the same output voltage.

The theoretical efficiency was calculated according to the following equations:

$$\eta = \frac{P_{\text{out}} \cdot 100\%}{P_{\text{out}} + P_{\text{loss}}},\tag{51}$$

Fig. 16. Measured and theoretical converter efficiency as a function of the output power

$$P_{\text{loss}} = P_{\text{T1}} + P_{\text{T2}} + P_{\text{D}} + P_{\text{WIRE(T)}} + P_{\text{WIRE(R)}} + P_{\text{CORE(T)}} + P_{\text{CORE(R)}} + P_{\text{SNUB}},$$

(52)

where  $P_{\rm loss}$  is calculated power losses;  $P_{\rm T1}$ ,  $P_{\rm T2}$ ,  $P_{\rm D}$  are conduction losses in transistors and diode;  $P_{\rm WIRE(T)}$ ,  $P_{\rm WIRE(R)}$  are conduction losses in wires of tapped and resonant inductors;  $P_{\rm CORE(T)}=3$  W and  $P_{\rm CORE(R)}=1.5$  W are estimated power losses in cores of tapped and resonant inductors;  $P_{\rm SNUB}$  are power losses in snubbers.

The theoretical conduction losses in semiconductors and power losses in snubbers are given by:

$$P_{\rm T1} = I_{\rm T1(RMS)}^2 R_{\rm DS1(on)},$$

(53)

$$P_{\rm T2} = I_{\rm T2(RMS)}^2 R_{\rm DS2(on)},$$

(54)

$$P_{\rm D} = I_{\rm D(RMS)}^2 R_{\rm D} + I_{\rm o} V_{\rm TO},$$

(55)

$$P_{WIRE(T)} = I_{in(RMS)}^2 R_{PW} + I_{D(RMS)}^2 R_{SW},$$

(56)

$$P_{\text{WIRE(R)}} = I_{\text{D(RMS)}}^2 R_{Lr}, \tag{57}$$

$$P_{\text{SNUB}} = f_{\text{s}} \left( C_{\text{SNUB(T2)}} V_{\text{DS2(max)}}^2 + C_{\text{SNUB(D)}} V_{\text{D(max)}}^2 \right) / 2,$$

(58)

where  $R_{\rm DS1(on)}=29~{\rm m}\Omega$ ,  $R_{\rm DS2(on)}=12~{\rm m}\Omega$  are drain-source on resistances of switches  $T_1$ ,  $T_2$ ;  $V_{TO}=0.93~{\rm V}$  is the threshold voltage of diode D;  $R_D=101~{\rm m}\Omega$  is the series resistance of diode D;  $R_{PW}=12~{\rm m}\Omega$  and  $R_{SW}=150~{\rm m}\Omega$  are primary and secondary windings resistances;  $R_{Lr}=50~{\rm m}\Omega$  is resonant inductor resistance.

At low output power, efficiency is lower and increases with the load. The decrease in efficiency at low power levels is due to losses in inductors cores. Deformed currents in DCM increase its RMS values (Eqs. (40–48)) which causes the share of conduction losses in the total power losses at low power to remain high. For example, the calculated conduction losses for  $P_{\rm o} = 300 \text{ W}$  and  $V_{\rm in} = 40 \text{ V}$  in semiconductors power components and inductors wires are 5.5 W (1.8% of output power), for  $P_{\rm o} = 75 \text{ W}$  and  $V_{\rm in} = 40 \text{ V}$  are 1.1 W (1.5% of output power). The highest efficiency  $\eta = 94.7\%$  was obtained with the output power  $P_0 = 260$  W and the input voltage  $V_{in} = 50$  V. The lowest efficiency 90.7% was obtained for the input voltage  $V_{in} = 30 \text{ V}$ and the output power  $P_0 = 75$  W. Reducing the input voltage (increasing the voltage transformation ratio) while maintaining a constant voltage at the output reduces the efficiency of energy conversion.

### 8. Performance comparison

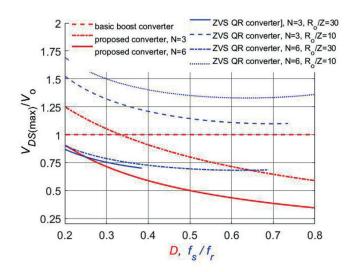

Figure 17 shows the comparison of the theoretical voltage conversion ratio between the proposed converter and other converters. The proposed converter uses a soft switching technique similar to the basic ZVS QR boost converter with a tapped inductor [8, 15]. However, in [8] the maximum voltage on the main transistor and the voltage conversion ratio are high and depend on the output resistance  $R_0$  and the characteristic impedance Z. Furthermore, the transistor is soft switched only in a narrow power range. In the proposed converter, by using an additional transistor connected in series with the resonant capacitor, the main transistor is soft switching in a wide output power range; the maximum voltage on the main transistor is lower and the voltage conversion ratio is higher.

Fig. 17. Comparison of the proposed converter, basic boost converter and [8] converters with regard to voltage conversion ratio

Fig. 18. Comparison of the proposed converter, basic boost converter and [8] converters with regard to transistor voltage stress

Figure 18 shows the comparison of the theoretical main switch voltage stress between the proposed converter and other converters.

Table 2 shows a comparison of performance parameters between the proposed converter, basic boost converter and ZVS quasi-resonant boost converter with a tapped inductor [8]. In the proposed converter relative frequency  $(f_s/f_r)$  may be much lower than [8], which ensures much lower conduction losses. Furthermore, in the proposed converter the voltage conversion

Table 2

Performance comparison

| Converter                                | Basic boost converter | Converter in [8]                                  | Proposed converter    |

|------------------------------------------|-----------------------|---------------------------------------------------|-----------------------|

| Active switches                          | 1                     | 1                                                 | 2                     |

| Diodes                                   | 1                     | 1                                                 | 1                     |

| Voltage conversion ratio                 | $\frac{1}{1-D}$       | $f\begin{pmatrix} Q, n, \\ f_s/f_r \end{pmatrix}$ | $\frac{ND+1}{1-D}^*$  |

| Voltage stress of main active switch     | $V_{out}$             | $f\begin{pmatrix} Q, n, \\ f_s/f_r \end{pmatrix}$ | $\frac{2V_{in}}{1-D}$ |

| Voltage stress of output diode           | $V_{out}$             | $f\begin{pmatrix} Q, n, \\ f_s/f_r \end{pmatrix}$ | $V_{out} + nV_{in}$   |

| Reverse recovery problem                 | serious               | small                                             | small                 |

| Conduction losses                        | medium                | large                                             | small                 |

| Turn-on condition of main active switch  | hard                  | ZVS                                               | ZCS*,<br>ZVS**        |

| Turn-off condition of main active switch | hard                  | ZVS                                               | ZVS                   |

\*CCM, \*\*DCM

ratio and the voltage stress on power semiconductors do not depend on the parameters of the resonant circuit and the output resistance.

### 9. Conclusion

This paper presents a discussion of a novel cost-effective quasi-resonant boost converter with a tapped inductor. This converter combines zero voltage quasi-resonant techniques and different conduction modes with the possibility to obtain a high voltage conversion ratio. This results in high converter efficiency and the soft switching of transistors in the whole output power range. Simultaneously, it is built using a small number of power components and the tapped inductor with a small number of turns.

This topology utilizes the tapped inductor, reduces voltage stress on switches and increases the voltage conversion ratio. However, there exist voltage overshoots caused by leakage inductance in the practical circuit. It induces additional voltage stresses and necessitates the use of switches with higher blocking voltage, leading to more losses and reduced efficiency. The proposed converter effectively uses leakage inductance by making it part of the quasi-resonant circuit. As a result, leakage inductance is no longer a problem, and it actually helps to provide zero-voltage and zero-current switching.

The examined and described non-isolated DC/DC converter can operate at a high voltage conversion ratio in such a manner as transformer-isolated converters, without the necessity to work at extreme values of the duty cycle.

The ZVS-AERC converter, in comparison to its counterparts with a transistor switched with fixed an on/off time, needs one additional transistor connected in series with the resonant capacitor to increase the resonant frequency with regard to the switching frequency and, consequently, to reduce the conduction losses. In the proposed converter, voltage rating of main transistor, size of resonant inductor and conduction losses in resonant capacitor are reduced, which is why these systems can achieve higher efficiency then in [8] at the significant output power.

The handling of very large input currents from low-input voltage sources remains a practical issue for high power applications

Finally, it was definitely confirmed that the proposed converter has a simple structure, is low-cost and compact, and offers high efficiency and high frequency soft-switching at the expense of minimum circuit components.

**Acknowledgements.** This work was supported by the Ministry of Science and Higher Education in Poland under work No. WZ/WE-IA/6/2020.

### REFERENCES

- [1] M. Forouzesh, Y.P. Siwakoti, S.A. Gorji, F. Blaabjerg, and B. Lehman, "Step-Up DC-DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications", *IEEE Trans. Power Electron.* 32(12), 9143–9178 (2017), doi: 10.1109/TPEL.2017.2652318.

- [2] W. Li and X. He, "Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications", *IEEE Trans. Ind. Electron.* 58(4), 1239–1250 (2011), doi: 10.1109/TIE.2010.2049715.

- [3] H. Liu, H. Hu, H. Wu, Y. Xing, and I. Batarseh, "Overview of High-Step-Up Coupled-Inductor Boost Converters", *IEEE IEEE J. Emerg. Sel. Top. Power Electron.* 4(2), 689–704 (2016), doi: 10.1109/JESTPE.2016.2532930.

- [4] A. Tomaszuk and A. Krupa, "High efficiency high step-up DC/DC converters a review", *Bull. Pol. Ac.: Tech.* 59(4), 475–483 (2011), doi: 10.2478/v10175-011-0059-1.

- [5] W. Janke, M. Bączek, and J. Kraśniewski, "Input characteristics of a non-ideal DC-DC flyback converter", *Bull. Pol. Ac.: Tech.* 67(5), 841–849 (2019), doi: 10.24425/bpasts.2019.130884.

- [6] F.C. Lee, "High-frequency quasi-resonant converter technologies", *Proc. IEEE* 76(4), 377–390 (1988), doi: 10.1109/5.4424.

- [7] W.A. Tabisz, P.M. Gradzki, and F.C.Y. Lee, "Zero-voltage-switched quasi-resonant buck and flyback converters-experimental results at 10 MHz", *IEEE Trans. Power Electron.* 4(2), 194–204, 1989, doi: 10.1109/63.24904.

- [8] M. Harasimczuk and A. Borchert, "Single switch quasi-resonant ZVS converter with tapped inductor", Prz. Elektrotechniczny 3, 44–48 (2018).

- [9] S. Sathyan, H.M. Suryawanshi, M.S. Ballal, and A.B. Shitole, "Soft-Switching DC-DC Converter for Distributed Energy Sources With High Step-Up Voltage Capability", *IEEE Trans. Ind. Electron.* 62(11), 7039–7050 (2015), doi: 10.1109/TIE.2015.2448515.

- [10] T.F. Wu, Y.S. Lai, J.C. Hung, and Y.M. Chen, "Boost Converter With Coupled Inductors and Buck- Boost Type of Active Clamp", *IEEE Trans. Ind. Electron.* 55(1), 154–162 (2008), doi: 10.1109/TIE.2007.903925.

- [11] J.H. Yi, W. Choi, and B.H. Cho, "Zero-Voltage-Transition Interleaved Boost Converter With an Auxiliary Coupled Inductor", *IEEE Trans. Power Electron.* 32(8), 5917–5930 (2017), doi: 10.1109/TPEL.2016.2614843.

- [12] Y. Chen, Z. Li, and R. Liang, "A Novel Soft-Switching Interleaved Coupled-Inductor Boost Converter With Only Single Auxiliary Circuit", *IEEE Trans. Power Electron.* 33(3), 2267–2281 (2018), doi: 10.1109/TPEL.2017.2692998.

- [13] R. Stala *et al.*, "A family of high-power multilevel switched capacitor-based resonant DC-DC converters operational parameters and novel concepts of topologies", *Bull. Pol. Ac.: Tech.* 65(5), 639–651 (2017).

- [14] M. Harasimczuk, "A QR-ZCS Boost Converter With Tapped Inductor and Active Edge-Resonant Cell", *IEEE Trans. Power Electron.* 35(12), 13085–13095 (2020), doi: 10.1109/TPEL.2020.2991363.

- [15] M. Harasimczuk, "Przekształtniki podwyższające napięcie z dławikami dzielonymi" PL Patent, Poland, P.423354, 2017.