ARCHIVES OF ELECTRICAL ENGINEERING

VOL. 71(4), pp. 1051 -1063 (2022)

DOI 10.24425/aee.2022.142124

# Design, development and verification of a new multilevel inverter for reduced power switches

BIDYUT MAHATO<sup>1</sup> <sup>□</sup> <sup>□</sup> MRINAL RANJAN<sup>2</sup>, PRADIPTA KUMAR PAL<sup>3</sup>, SANTOSH KUMAR GUPTA<sup>4</sup>, KAILASH KUMAR MAHTO<sup>2</sup>

<sup>1</sup>ABES Engineering College

Ghaziabad, UP – 201009, India

<sup>2</sup>Gaya College of Engineering

Gaya, Bihar – 823003, India

<sup>3</sup>Indian Institute of Technology (Indian School of Mines)

Dhanbad – 826004, India

<sup>4</sup>Government Engineering College

Siwan, Bihar – 841226, India

e-mail: <sup>™</sup>bidyut1990/mrinal10m255/santoshgupta1990/kailash8317}@gmail.com, pradipta.18dr0096@ee.iitism.ac.in

(Received: 27.05.2022, revised: 29.08.2022)

**Abstract:** Due to recent developments in the field of high-power and medium-voltage, the multilevel inverter has raised to such an extent owing to some of its amazing facts regarding harmonic spectrum, ease in control, reduced electromagnetic interference (EMI), filterless circuit, stress on power switches, common-mode voltage. This paper well describes a novel architecture of a single-phase multilevel inverter using a lesser number of overall components, especially the power switches. The proposed topology is generalized in the structure that can generate any number of voltage steps. A 7-level structure of the proposed topology is explained and is elaborately discussed. Simulation is carried out in MATLAB and corresponding experimental results verify the existence of the proposed multilevel inverter. The real-time experimental results were presented and are well verified by the simulation results for 7-level as well for 13-level across RL-Load. The nature of load current is also indicated as per the nature of load voltage. Nevertheless, the topology is further compared with some of the recent literature and found superior in each respect.

**Key words:** 7-level/13-level inverter, DC-AC converters, power-electronic switches, sinusoidal PWM

#### 1. Introduction

The multilevel inverter (MLI) is a power electronic device introduced in the year 1981, being the most emerging topic of research that produces arbitrary voltage output waveform with consuming required DC sources and power switches. The desired voltage at the output is attained by applying a particular switching arrangement on the available power switches [1]. The undesirable harmonics in the output voltage and current waveforms are not eliminated in the traditional inverters resulting in excessive power loss [2, 3]. Some of the foremost applications of MLIs are in flexible AC transmission systems (FACTs) [4], renewable energy systems [5], electric drives [6], and active filters [7]. The basic and most renowned multilevel inverters are: neutral-point clamped (NPC), flying capacitor (FC), and cascaded H-bridge (CHB) [8]. This above-mentioned technology can generate the output voltage with higher power quality, lower total harmonic distortion (THD), and a lower electromagnetic interface [9]. Further, MLI configurations are categorized as symmetrical and asymmetrical configurations depending on the magnitudes of DC sources [10] whereas symmetrical configuration of MLIs comprises DC sources of equal magnitudes and asymmetrical configuration of MLIs comprises DC sources of unequal magnitudes. A treaty lies between both the configurations (symmetrical and asymmetrical DC sources) that the asymmetrical MLI stands better in terms of generated voltage levels for the same number of required power switches whereas symmetrical MLI stands better in terms of a variety of required DC sources. The quantity of power switches and DC sources is the soul to achieve a sinusoidal waveform. An increase in the number of power switches is considered one of the key disadvantages of multilevel inverters as it reflects in cost enhancement and complexity in control thus reducing the overall reliability. However, the possibility of the occurrence of the fault between the power switches is increasing day by day where 21% of faults arise in power semiconductor switches and faults in the module include 34% of total failures in a converter system [11].

Reduced components MLI inverter is thereby introduced by researchers to generate voltage levels and keep trying to reduce the power switches. Both the symmetric and asymmetric values of DC sources are executed for the proposed topology. A 7-level symmetrical and 13-level asymmetrical value of DC sources is designed and tested in a MATLAB environment. Nevertheless, an experimental setup is designed and executed in the laboratory. Simulation results are obtained through MATLAB and are then verified by the corresponding experimental results considering RL-Load. In addition, various recent topologies suggested in [12–21] are compared with the proposed topology having the best asymmetric voltage ratio (1:2:4), and hence can be increased similarly. The limitation of the proposed topology is many required DC sources.

## 2. Proposed topology

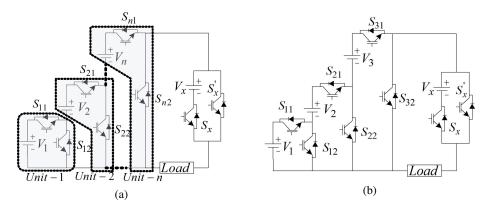

Figure 1(a): the proposed MLI, as shown in, is generalized and thus it can generate levels as per the requirement of the application. Units are added, as shown in Fig. 1(a), to generate higher voltage levels in the output. One DC source with two power switches is required for a unit. Figure 1(b) shows the proposed topology that can generate 7-level/9-level/11-level/13-level/15-level using different values of DC sources and this structure can be further extended by adding the aforementioned units. Unit-1 contains two power switches ( $S_{11}$  and  $S_{12}$ ) and one

DC source  $(V_1)$ . Unit-2 contains two power switches  $(S_{21} \text{ and } S_{22})$  with one DC source  $(V_2)$ . Unit-3 contains two power switches  $(S_{31} \text{ and } S_{32})$  with one DC source  $(V_3)$ . Unit-n contains two power switches  $(S_{n1} \text{ and } S_{n2})$  with one DC source  $(V_n)$ . A noticeable point shows that there are only two switches  $(S_x \text{ and } S_x')$  with a DC source  $(V_x)$  needed instead of an H-bridge where  $V_x$  is the addition of the total voltage in units. All the power switches employed in the entire circuit are unidirectional.

Design, development and verification of a new multilevel inverter

Fig. 1. Generalized structure of proposed topology (a); proposed topology with different voltage-levels (b)

$$V_1 = V_2 = V_3 = V_{dc}, \quad V_x = 3V_{dc},$$

(1)

(ii) 9-level

$$V_1 = V_{dc}$$

,  $V_2 = V_{dc}$ ,  $V_3 = 2V_{dc}$ ,  $V_x = 4V_{dc}$ , (2)

(iii) 11-level

$$V_1 = V_{dc}, \quad V_2 = 2V_{dc}, \quad V_3 = 2V_{dc}, \quad V_x = 5V_{dc},$$

(3)

(iv) 13-level

$$V_1 = V_{dc}, \quad V_2 = 2V_{dc}, \quad V_3 = 3V_{dc}, \quad V_x = 6V_{dc},$$

(4)

(v) 15-level

$$V_1 = V_{dc}$$

,  $V_2 = 2V_{dc}$ ,  $V_3 = 4V_{dc}$ ,  $V_x = 7V_{dc}$ . (5)

The magnitude of voltage sources can be set as symmetrical as well as asymmetrical. The attractiveness of the proposed MLI structure confirms its operation for the binary ratio, i.e.,  $1:2:4:8:\ldots:2^{N_{\rm dc}-1}$ , where  $N_{\rm dc}$  symbolizes the number of DC sources. For example, 3-level output voltage is offered with one unit consisting of one DC source  $(V_1 = V_{\rm dc})$ , where  $V_x$  is a DC source with a total magnitude of DC source  $(V_x = V_{\rm dc})$ . In addition, further next unit (Unit-2) having one DC source  $(V_2 = 2V_{\rm dc})$  is added in addition to the earlier DC source  $(V_1 = V_{\rm dc})$  of Unit-1. The magnitude of the DC source,  $V_x = 3V_{\rm dc}$  changes magnitude with the addition of each unit. Next to 3-level, 7-level, 15-level, 31-level, and so on, voltage levels are obtained with every time change in magnitude of DC source i.e.,  $V_x = 3V_{\rm dc}$ ,  $V_x = 7V_{\rm dc}$ ,  $V_x = 15V_{\rm dc}$ ,  $V_x = 31V_{\rm dc}$  and so on respectively.

### 3. Modes of operation

The approach of the controller for the MLI proposed in this paper is the pulse width modulation (PWM) technique. In this simple and well-defined technique, triangular carriers are chosen, and a reference sine signal is compared to produce the corresponding pulse pattern of the power switches. Level-shifted PWM (LS-PWM) is chosen among some of the well-known control strategies, i.e., phase-shifted PWM [18], nearest-level control (NLC) [19], selective harmonic elimination (SHE) [20], LS-PWM [21], [22–25] to cultivate the pulses in MATLAB.

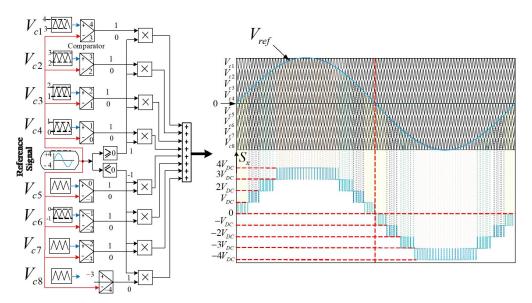

The PWM method generates several pulses with varying ON and OFF time duration or duty cycle such that the average value of the voltage over a half-cycle is varying sinusoidally. In order to obtain a suitable duty cycle for each switch, many modulation methods have been developed for the voltage source inverter (VSI). On the other hand, for the MLI, the lower-order harmonic components can be suppressed by increasing the number of the inverter voltage levels. Thus, for an MLI, a lesser switching frequency is usually preferred to lower the switching losses and improve efficiency. Figure 2 shows two popular modulation schemes and their corresponding output voltage or switching patterns. The level-shifted PWM (LS-PWM) technique is a high-frequency carrier-based PWM technique that generates a staircase voltage with a PWM pulse pattern, as observed from Fig. 2. This high-frequency PWM technique provides good harmonic profiles of the output voltage for an MLI with comparatively lesser voltage levels. The real-time simulator, dSPACE-1103 is used to produce the real-time pulses. Nevertheless, the switching pulses and switching table for the proposed inverter (symmetrical 7-level) are merged as well in Table 1. Pulse patterns obtained from the simulation as well as experimental results are shown in Fig. 3, respectively.

Fig. 2. Modulation of an MLI using SPWM technique for a 9-level inverter and its corresponding switching pattern

Design, development and verification of a new multilevel inverter

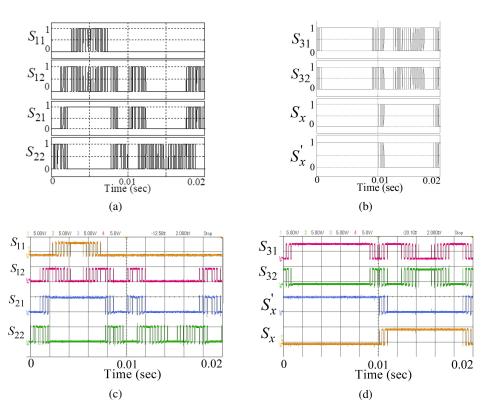

Fig. 3. Switching pulses of the power switches:  $S_{11}$ ,  $S_{12}$ ,  $S_{21}$  and  $S_{22}$  for simulation (a);  $S_{31}$ ,  $S_{32}$ ,  $S_x$  and  $S_x'$  for simulation (b);  $S_{11}$ ,  $S_{12}$ ,  $S_{21}$  and  $S_{22}$  for experimental (c);  $S_{31}$ ,  $S_{32}$ ,  $S_x$  and  $S_x'$  for experimental (d)

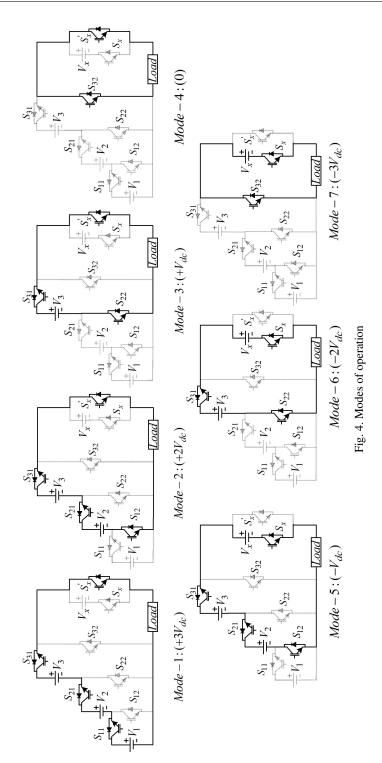

**Mode 1**: Power switches  $S_{11}$ ,  $S_{21}$ ,  $S_{31}$ , and  $S_x'$  are switched ON along with the three DC sources  $V_1 = 38$  V,  $V_2 = 38$  V, and  $V_3 = 38$  V generate +114 V, i.e., +3 $V_{\rm dc}$ .

**Mode 2**: Power switches  $S_{21}$ ,  $S_{31}$ ,  $S_{12}$ , and  $S_x'$  are switched ON along with the two DC sources  $V_2 = 38$  V and  $V_3 = 38$  V generating +76 V, i.e.,  $+2V_{dc}$ .

**Mode 3**: Power switches  $S_{22}$ ,  $S_{31}$ , and  $S_x'$  are switched ON along with only one DC source  $V_3 = 38$  V generates +38 V, i.e.,  $+V_{dc}$ .

**Mode 4**: Power switches  $S_{32}$  and  $S'_x$  are switched ON along with no DC source generating 0 V, i.e., zero.

**Mode 5**: Power switches  $S_{12}$ ,  $S_{21}$ ,  $S_{31}$ , and  $S_x$  are switched ON along with three DC sources,  $V_2 = 38 \text{ V}$ ,  $V_3 = 38 \text{ V}$ , and  $V_x = 114 \text{ V}$  generate -38 V, i.e.,  $-V_{dc}$ .

**Mode 6**: In this mode, power switches  $S_{22}$ ,  $S_{31}$ , and  $S_x$  are switched ON along with the two DC sources  $V_3 = 38$  V and  $V_x = 114$  V generating -76 V, i.e.,  $-2V_{dc}$ .

**Mode 7**: Power switches  $S_{32}$  and  $S_x$  are switched ON along with only one DC source,  $V_x = 114$  V generates -114 V, i.e.,  $-3V_{dc}$ .

Generation of the different voltage steps at different modes for the 7-level inverter has been addressed below and is portrayed in Fig. 4.

Design, development and verification of a new multilevel inverter

Table 1. Switching table for proposed 7-Level MLI ( $V_1 = V_2 = V_3 = V_{\rm dc}$ ) symmetrical

|                 | Voltage         |                 |                 |                 |                 |         |        |                   |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------|--------|-------------------|

| S <sub>11</sub> | S <sub>12</sub> | S <sub>21</sub> | S <sub>22</sub> | S <sub>31</sub> | S <sub>32</sub> | $S_{x}$ | $S_x'$ | levels            |

| 1               | 0               | 1               | 0               | 1               | 0               | 0       | 1      | +3V <sub>dc</sub> |

| 0               | 1               | 1               | 0               | 1               | 0               | 0       | 1      | +2V <sub>dc</sub> |

| 0               | 0               | 0               | 1               | 1               | 0               | 0       | 1      | +V <sub>dc</sub>  |

| 0               | 0               | 0               | 0               | 0               | 1               | 0       | 1      | 0                 |

| 0               | 1               | 1               | 0               | 1               | 0               | 1       | 0      | $-V_{ m dc}$      |

| 0               | 0               | 0               | 1               | 1               | 0               | 1       | 0      | $-2V_{\rm dc}$    |

| 0               | 0               | 0               | 0               | 0               | 1               | 1       | 0      | $3-3V_{\rm dc}$   |

## 4. Comparison with new topologies

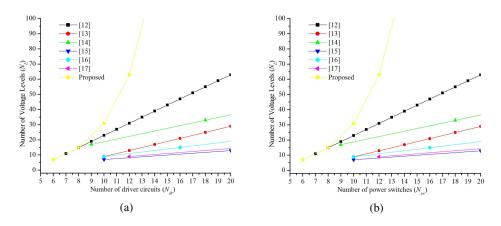

The generalized formulae are derived for all the required components i.e., a total number of DC sources ( $N_{\rm dc}$ ), power switches ( $N_{\rm sw}$ ), uni-directional switches ( $N_U$ ), bi-directional switches ( $N_B$ ) of the discussed topology are accorded with all the parameters of topologies studied in [12–17] that have been listed in Table 2. A comparison of the required components for the proposed MLI topology is made for the voltage ratio of 1:2:4:8.

Table 2. Generalized formulae of the required components for recently compared topologies and the proposed topology

| Types of MLI  | Components count         |                  |                   |                            |  |  |  |  |

|---------------|--------------------------|------------------|-------------------|----------------------------|--|--|--|--|

| Types of WILI | $(N_L)$                  | $(N_B)$          | $(N_U)$           | $(N_{ m dc})$              |  |  |  |  |

| [12]          | $(4N_{\rm sw} - 17)$     | $N_{\rm sw}$ – 6 | 6                 | $N_{\rm sw}-3$             |  |  |  |  |

| [13]          | $(2N_{\rm sw} - 11)$     | NA               | $N_{\rm sw}$      | <i>N</i> <sub>sw</sub> – 6 |  |  |  |  |

| [14]          | $(16N_{\rm sw} + 9)/9$   | $N_{\rm sw}/3$   | $2N_{\rm sw}/3$   | $4N_{\rm sw}/9$            |  |  |  |  |

| [15]          | $(3N_{\rm sw} + 4)/4$    | NA               | $N_{ m sw}$       | $3N_{\rm sw}/8$            |  |  |  |  |

| [16]          | $(N_{\rm sw}-1)$         | NA               | $N_{\mathrm{sw}}$ | $(N_{\rm sw} - 2)/2$       |  |  |  |  |

| [17]          | $(2N_{\rm sw} + 3)/3$    | NA               | $N_{\mathrm{sw}}$ | $N_{\rm sw}/4$             |  |  |  |  |

| Proposed      | $[2^{(N_{\rm sw}/2)}-1]$ | NA               | $N_{\mathrm{sw}}$ | $(N_{\rm sw} - 2)/2$       |  |  |  |  |

Besides, the graph is plotted (Fig. 5) between voltage levels ( $N_L$ ) against the power switches ( $N_{\rm sw}$ ) as well as driver circuits ( $N_{\rm dr}$ ). Thus, it is concluded that the reduced power switches reduce the driver circuits thereby reducing maintenance for the circuit, easier to implement, lower cost, and less complex.

Fig. 5. Graph showing the comparison b/w proposed MLI and other existing MLIs:  $N_L$  versus  $N_{\rm dr}$  (a);  $N_L$  versus  $N_{\rm sw}$  (b)

## 5. Simulation and experimental results

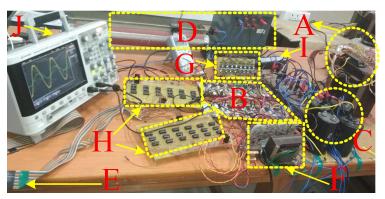

Figure 6 schematically explains the experimental set-up of the proposed 13-level inverter.

Fig. 6. Experimental set-up of the proposed 13-level inverter consists of:  $\bf A$  – transformer (220 V/5 A) and rectifier capacitor based DC source;  $\bf B$  – IGBT-based 13-level MLI with driver ICs;  $\bf C$  – electrolytic capacitors (400 V, 4700  $\mu$ F);  $\bf D$  – R–L load ( $\bf R$  = 60  $\bf \Omega$  and  $\bf L$  = 100 mH);  $\bf E$  – flat ribbon cable from DS1103 connector;  $\bf F$  and  $\bf G$  – isolated supply for driver ICs (220 V/20 V, 500 mA) and delay circuit (220 V/5 V);  $\bf H$  – delay circuit board;  $\bf I$  – current probe (1146B, 100 kHz/100 A) and  $\bf J$  – DSO-X 2024A

The inverter circuit is constituted of:

- a) a single 1:1 isolation transformer rated at 220 V/5 A, 50 Hz (supplied from an auto-transformer connected to the primary, and a rectifier-capacitor arrangement connected at the secondary),

- b) proposed 13-level inverter circuit constituting of 8 numbers of IGBT switches and gate drivers mounted on the heat sink,

c) four electrolytic capacitors for the 13-level inverter (two electrolytic capacitors for the basic 9-level module) individually rated at 400 V,  $4\,700\,\mu F$ ,

Design, development and verification of a new multilevel inverter

- d) R-L load with  $R = 60 \Omega$  and L = 100 mH,

- e) flat ribbon cable connectors for fetching gate pulses from the connector of DS1103 based controller,

- f) two numbers of 220 V/20 V, 500 mA isolation transformer for 8 numbers of gate driver power supply for the 13-level inverter and a single 220 V/20 V isolation transformer used for supplying 8 numbers of gate drivers for the proposed 9-level inverter,

- g) rectifier, capacitor and linear voltage regulator (LM series) connected at the secondary of the individual 220 V/20 V transformer (used for gate drivers) for generating constant +20 V DC supply to the gate drivers,

- h) external delay circuit board used to provide delayed pulses to the gate drivers to avoid short circuiting of IGBT switches, the delay used is  $2 \mu s$ ,

- i) an extra 220 V/5 V isolation transformer with rectifier filter arrangement is required to provide +5 V DC power supply for proper functioning of the digital ICs used in the external delay board and also to protect the digital ICs from the 220 V power supply voltages,

- j) four channel DSO-X 2024A from KEYSIGHT used for calibrating various results obtained from the 7-level/13-level SC-MLI.

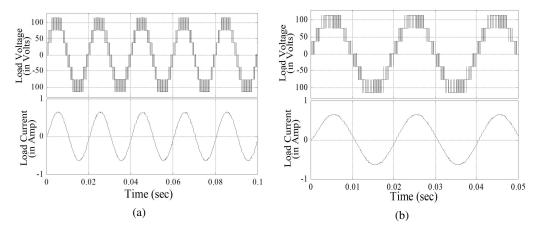

The Proposed MLI for symmetric voltage (7-Level inverter) is developed and being tested in a MATLAB environment with the DC sources of magnitude as 38 V, i.e.,  $V_l = V_2 = V_3 = V_{\rm dc} = 38$  V and  $V_x = 114$  V. Thus, the peak voltage of output (maximum) is +114 V and the peak voltage of output (minimum) is -114 V. The simulation is then carried out with RL-Load, R = 170  $\Omega$ , L = 100 mH. The results of voltage and current (load) are presented for 5-cycles and 2.5-cycles as represented in Figs. 7(a) and 7(b), respectively.

Fig. 7. Simulation results of 7-level: load voltage and current (5-cycles) (a); load voltage and current (2.5-cycles) (b)

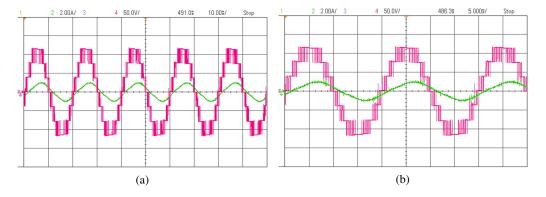

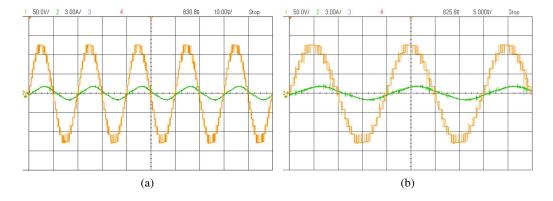

An experimental set-up is also executed for the same, i.e., for a 7-level inverter (symmetrical) where the experimental results are verified by the simulation result as shown in Figs. 8(a) (2.5-

cycles) and 8(b) (5-cycles), respectively. Moreover, a 13-level inverter is considered by choosing the magnitude of DC voltage in the ratio of 1:2:3, i.e.,  $V_1 = 21 \text{ V}, V_2 = 42 \text{ V}, V_3 = 63 \text{ V}, V_x = 126 \text{ V}$  thereby generating +126 V as the peak of output voltage (maximum) and -126 V as the peak of output voltage (minimum) for load remaining the same, i.e.,  $R = 170 \Omega$ , L = 100 mH. Figures 9(a) and 9(b) show the load voltage and current for 5-cycles and 2.5-cycles respectively. All the results (symmetrical and asymmetrical) are incorporated to prove the effectiveness of the proposed topology.

Fig. 8. Experimental results of 7-level: load voltage and current (5-cycles) (a); load voltage and current (2.5-cycles) (b)

Fig. 9. Experimental results of 13-level: load voltage and current (5-cycles) (a); load voltage and current (2.5-cycles) (b)

The voltage waveform of the proposed 13-level inverter under dynamic conditions like variation of  $m_i$  is shown in Fig. 10. It is observed that for different values of  $m_i$  the proposed 13-level inverter generates three levels, five levels, seven levels, nine levels, and 11 levels respectively.

1061

Fig. 10. Experimental results of output voltage and current of the proposed 13-level inverter for the transition of  $m_i$  from 0.15 to 1.0

#### 6. Conclusions

This paper presents a novel and generalized topology which can be extended by adding the units. Based on the proposed MLI structure, 7-level (symmetrical) and 13-level (asymmetrical) inverters are simulated, and the results are experimentally verified with RL-Load. The topology shows better outcomes in terms of overall required components. The generalized formula for each required components is also derived for the proposed topology and suggested recent MLI topologies. The proposed topology was found better in terms of the economic cost, simpler circuit, and control, less maintenance, and less space requirement. Thus, the proposed reduced switch MLI is concluded to be better than the newly suggested MLIs.

#### References

- [1] Belkacem R.E., Benzid R., Bouguechal N., *Multilevel inverter with optimal THD through the firefly algorithm*, Archives of Electrical Engineering, vol. 66, no. 1, pp. 141–154 (2017), DOI: 10.1515/aee-2017-0010.

- [2] Rodríguez J., Lai J.S., Peng F.Z., Multilevel inverters: A survey of topologies controls and applications, IEEE Transactionson Industrial Electronics, vol. 49, no. 4, pp. 724–38 (2002), DOI: 10.1109/ TIE.2002.801052.

- [3] Jha K.K., Mahato B., Prakash P., Active power factor correction for rectifier using micro-controller, 3rd International Conference on Recent Advances in Information Technology, ISM Dhanbad, India, pp. 331–336 (2016), DOI: 10.1109/RAIT.2016.7507926.

- [4] Sotoodeh P., Miller R.D., *Design and implementation of an 11-level inverter with FACTS capability for distributed energy systems*, IEEE Journal of emerging and selected topics in power electronics, vol. 2, no. 1, pp. 87–96 (2014), DOI: 10.1109/JESTPE.2013.2293311.

- [5] Xiao B., Hang J., Mei J. et al., Modular cascaded H-bridge multilevel PV inverter with distributed MPPT for grid-connected applications, IEEE Transactions on Industry Applications, vol. 51, no. 2, pp. 1722–1731 (2015), DOI: 10.1109/TIA.2014.2354396.

- [6] Hagiwara M., Hasegawa M., Akagi H., *Start-up and low-speed operation of an electric motor driven by a modular multilevel cascade inverter*, IEEE Transactions on Industry Applications, vol. 49, no. 4, pp. 1556–1565 (2013), DOI: 10.1109/TIA.2013.2256331.

- [7] Varschavsky A., Dixon J., Rotella M. *et al.*, *Cascaded nine-level inverter for hybrid-series active power filter using industrial controller*, IEEE Transactions on Industrial Electronics, vol. 57, no. 8, pp. 2761–2767 (2010), DOI: 10.1109/TIE.2009.2034185.

- [8] Malinowski M., Gopakumar K., Rodriguez J. et al., A survey on cascaded multilevel inverters, IEEE Transactions on Industrial Electronics, vol. 57, no. 7, pp. 2197–2206 (2010), DOI: 10.1109/TIE.2009. 2030767

- [9] Wang K., Li Y., Zheng Z. et al., Voltage balancing and fluctuation-suppression methods of floating capacitors in a new modular multilevel converter, IEEE Transactions on Industrial Electronics, vol. 60, no. 5, pp. 1943–1954 (2013), DOI: 10.1109/TIE.2012.2201433.

- [10] Vazquez S., Leon J.I., Franquelo L.G., Padilla J.J., Carrasco J.M., DC-voltage-ratio control strategy for multilevel cascaded converters fed with a single DC source, IEEE Transactions on Industrial Electronics, vol. 56, no. 7, pp. 2513–2521 (2009), DOI: 10.1109/TIE.2009.2017549.

- [11] Yang S., Xiang D., Bryant A. et al., Condition monitoring for device reliability in power electronic converters: A review, IEEE Transactions on Power Electronics, vol. 25, no. 11, pp. 2734–2752 (2010), DOI: 10.1109/TPEL.2010.2049377.

- [12] Agarwal R., Jain S., Multilevel inverter for interfacing renewable energy sources with low/medium- and high-voltage grids, IET Renew. Power Gener., vol. 11, no. 14, pp. 1822–1831 (2017), DOI: 10.1049/ietrpg.2016.1034.

- [13] Arun M., Noel M.M., *Crisscross switched multilevel inverter using cascaded semi-half-bridge cells*, IET Power Electron., vol. 11, no. 1, pp. 23–32 (2018), DOI: 10.1049/iet-pel.2016.0644.

- [14] Samadaei E., Sheikholeslami A., Gholamian S.A., Adabi J., A Square T-Type (ST-Type) Module for Asymmetrical Multilevel Inverters, IEEE Transactions on Power Electronics, vol. 33, no. 2, pp. 987–996 (2018), DOI: 10.1109/TPEL.2017.2675381.

- [15] Lee S.S., Sidorov M., Idris N.R.N., Heng Y.E., A Symmetrical Cascaded Compact-Module Multilevel Inverter (CCM-MLI) with Pulsewidth Modulation, IEEE Transactions on Industrial Electronics, vol. 65, no. 6, pp. 4631–4639 (2018), DOI: 10.1109/TIE.2017.2772209.

- [16] Lee S.S., Sidorov M., Idris N.R.N., Heng Y.E., Hybrid Cascaded Multilevel Inverter (HCMLI) with Improved Symmetrical 4-Level Submodule, IEEE Transactions on Power Electronics, vol. 33, no. 2, pp. 932–935 (2018), DOI: 10.1109/TPEL.2017.2726087.

- [17] Lee S.S., Single-Stage Switched-Capacitor Module (S3CM) Topology for Cascaded Multilevel Inverter, IEEE Transactions on Industrial Electronics, pp. 1–1 (2018), DOI: 10.1109/TPEL.2018.2805685.

- [18] Siddique M.D., Mekhilef S., Shah N.M., Memon M.A., *Optimal design of a new cascaded multilevel inverter topology with reduced switch count*, IEEE Access, vol. 7, pp. 24498–24510 2019, DOI: 10.1109/ACCESS.2019.2890872.

- [19] Siddique M.D., Mekhilef S., Shah N.M., Ali J.S.M., Blaabjerg F., *A new switched capacitor 7L inverter with triple voltage gain and low voltage stress*, IEEE Transactions on Circuits Syst. II, Exp. Briefs, vol. 67, no. 7, pp. 1294–1298 (2020), DOI: 10.1109/TCSII.2019.2932480.

- [20] Hashfi T.B., Mekhilef S., Mubin M., Seyedmahmoudian M., Horan B., Stojcevski A., *Adaptive carrier-based pdpwm control for modular multilevel converter with fault-tolerant capability*, IEEE Access, vol. 8, pp. 26739–26748 (2020), DOI: 10.1109/ACCESS.2020.2970725.

Vol. 71 (2022)

Design, development and verification of a new multilevel inverter

1063

- [21] Siddique M.D., Ali J.S.M., Mekhilef S., Mustafa A., Sandeep N., Almakhles D., *Reduced switch count based single source 7L boost inverter topology*, IEEE Transactions on Circuits Syst. II, Exp. Briefs, vol. 67, no. 12, pp. 3252–3256 (2020), DOI: 10.1109/TCSII.2020.2988090.

- [22] Jana K.C., Biswas S.K., Chowdhury S.K., *Dual reference phase shifted pulse width modulation technique for a N-level inverter-based grid connected solar photovoltaic system*, IET Renew. Power Gener., vol. 10, no. 7, pp. 928–935 (2016), DOI: 10.1049/iet-rpg.2015.0393.

- [23] Mahato B., Raushan R., Jana K.C., *Comparative Study of Asymmetrical Configuration of Multilevel Inverter for Different Levels*, 3rd International Conference on Recent Advances in Information Technology, ISM Dhanbad, India, pp. 300–303 (2016), DOI: 10.1109/RAIT.2016.7507920.

- [24] Dahidah M.S.A., Konstantinou G., Agelidus V.G., *A Review of Multilevel Selective Harmonic Elimination PWM: Formulations, Solving Algorithms, Implementation and Applications*, IEEE Transactions on Power Electronics, vol. 30, no. 8, pp. 4091–4106 (2015), DOI: 10.1109/TPEL.2014.2355226.

- [25] Kumar C., Mahato B. *et al.*, *Comprehensive study of various configurations of three-phase Multi-level inverter for different levels*, 3rd International Conference on Recent Advances in Information Technology, ISM Dhanbad, India, pp. 310–315 (2016), DOI: 10.1109/RAIT.2016.7507922.